Difference between revisions of "Clock generator (CLOCK)"

(Created page with "= LogicPool (CLOCK) = A clock can be implemented using the GATEGEN VHDL modul, due to this the address and register map is the same as by the GATEGEN == LabVIEW Vi == === ...") |

(→LogicPool (CLOCK)) |

||

| Line 1: | Line 1: | ||

= LogicPool (CLOCK) = | = LogicPool (CLOCK) = | ||

| − | A clock can be implemented using the GATEGEN VHDL | + | A clock can be implemented using the GATEGEN VHDL module, due to this the address and register map is the same as by the GATEGEN |

== LabVIEW Vi == | == LabVIEW Vi == | ||

Revision as of 10:23, 10 May 2016

Contents

LogicPool (CLOCK)

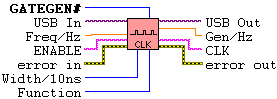

A clock can be implemented using the GATEGEN VHDL module, due to this the address and register map is the same as by the GATEGEN

LabVIEW Vi

CLOCK.vi

Template VI for new designs

Introduction.

The meaning of almost inputs and outputs of this Vi depends on the input "Function". The global inputs and outputs does not depend on the "function" input:

Glogal Inputs

DIO_HV#: number of HV digital output to be accesed (1..255).

USB In: Handle to the LogicBox (create by open.vi), if not connected will take a global. parameter, this only works with one LogicBox at a time.

error in: error handling input

Global Outputs

USB out: Handle to the LogicBox.

error out: error handling output

Functions

Connect: enable, configurate and set input/value of the HV digital output.

Inputs:

"DO" : set the signal number which will drive the output, this signal can be set or clear

manually using the module "B_S.vi" (Bool to Signal).

"DI" : get the signal number of which drives this input.

Get Status: the cicuitry of the digital output can detect two errors, under voltage or logic state

undifined. Only the first 8 channels support this features

Input: "Channel": number of channel to be configured

Output: Output Status

Set DO: set the signal number which will drive the output, this signal can be set or clear manually

using the module "B_S.vi" (Bool to Signal).

Input: "Channel": number of channel to be configured

"DO" set the signal number which will set the output value.

Example VIs

SU7XX_XX_test.vi