Difference between revisions of "SU741"

m |

(→Front panel) |

||

| (44 intermediate revisions by 3 users not shown) | |||

| Line 1: | Line 1: | ||

| + | = Description = | ||

| + | |||

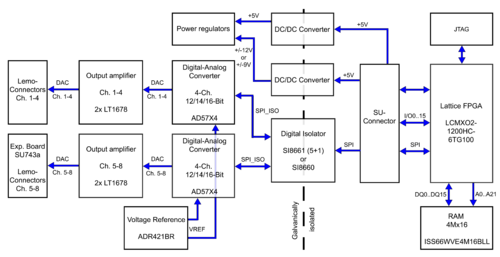

| + | This module is a Digital to analog converter with 8 isolated channels and integrated RAM (4M x 16-bit) memory. It is populated with a tiny FPGA to generate voltage sequences. | ||

| + | |||

| + | Two DACs AD57X4 from Analog Devices were used, this family consist of three DACs with 12, 14 and 16-bit resolution. They can operate from single-supply voltages from +4.5 V up to +16.5 V or dual-supply voltages from ±4.5 V up to ±16.5 V. Nominal full-scaleoutput range is software-selectable from +5 V, +10 V, +10.8 V,±5 V, ±10 V, or ±10.8 V. The SU741 power supply will be customized for each application if you do not need to work with the maximal output range. The DAC uses a serial interface that operates at 30 MHz clock rates. Double buffering allows the simultaneous updating of all DACs channels. | ||

| + | |||

| + | = Block Diagram = | ||

| + | |||

| + | |||

| + | [[File:SU741 Block Diagram.png | 500px]] | ||

| + | |||

| + | = Front panel = | ||

| + | |||

| + | [[File:SU741_front_panel.png]] | ||

| + | |||

| + | = Back Connector = | ||

| + | |||

SU741 pin table (direction shown for the SU board!) | SU741 pin table (direction shown for the SU board!) | ||

| Line 29: | Line 46: | ||

- the memory is 4M x 16 instead of 8M x 16 | - the memory is 4M x 16 instead of 8M x 16 | ||

| − | |||

- there is a direct connection to the SPI and DAC interface | - there is a direct connection to the SPI and DAC interface | ||

| + | - no HISTO and CRE signals on the SU-connector (CRE was anyway not used) | ||

| + | - Addr2 is now Sync (10 MHz for time measurement), therefore 2 instead of 4 address pointers | ||

| + | - DAC signal has another meaning (was anyway not used before) | ||

| + | - control/command/status registers - still not fully defined and implemented, used for start/pause/stop and more. | ||

| − | + | = Power consumption = | |

| − | + | +5V -> 150 mA | |

| − | + | = Measurement = | |

| − | |||

| + | = Others = | ||

Interface: | Interface: | ||

| Line 67: | Line 87: | ||

sync is a slow clock (10 MHz) for the time measurement | sync is a slow clock (10 MHz) for the time measurement | ||

| − | Bit positions writing to CR[ | + | Bit positions writing to CR[3] : 0 : start from the beginning or continue, 1 : pause, 2 : continue, 3 : stop ... |

DI/DO 0..15 | DI/DO 0..15 | ||

read_n 16 | read_n 16 | ||

| Line 79: | Line 99: | ||

dac 25 | dac 25 | ||

| + | |||

| + | Status register: | ||

| + | |||

| + | Read from CR[3]: | ||

| + | |||

| + | bits 2..0 : state machine communication with LogicBox with states: idle(0), latch_cmd(1), read_ac(2), write_ac(3), read_ram(4), write_ram(5), finish(6) | ||

| + | bits 6..4 : state machine read/write to PSRAM with states: idle(0), read_a(1), read_d(2), read_l(3), write_a(4), write_d(5), finish(6) | ||

| + | bits 11..8 : state machine of the sequencer with states: idle(0), sent_ram_rq(1), read_tmH(2), read_tmL(3), read_dvH(4), read_dvL(5), read_dac_dmc(6), check_mask(7), read_dac(8), ldac_soft(9), st_pause(10), wait_dt(11), check_for_pause_stop(12) | ||

How to operate: | How to operate: | ||

| Line 86: | Line 114: | ||

2) write the memory content with address autoincrement using e.g. AC[1] | 2) write the memory content with address autoincrement using e.g. AC[1] | ||

| − | 3) start the sequency by writing to the CR[ | + | 3) start the sequency by writing 0 to the CR[3] |

4) later reading status from CR is allowed, but memory read/write is blocked while running the sequence | 4) later reading status from CR is allowed, but memory read/write is blocked while running the sequence | ||

| Line 113: | Line 141: | ||

command = 3 : DAC output register, generate LDAC immediately | command = 3 : DAC output register, generate LDAC immediately | ||

| + | < DAC output LSB non-zero bit in mask > | ||

| + | ... | ||

< DAC output MSB non-zero bit in mask > | < DAC output MSB non-zero bit in mask > | ||

| − | |||

| − | |||

| Line 122: | Line 150: | ||

Example: | Example: | ||

| − | + | Data Comment | |

| − | + | X"0000", -- div ratio 1 | |

| − | + | X"0001", | |

| − | + | X"4011", -- control mask 0x11 | |

| − | + | X"200F", -- power up all 4 | |

| − | + | X"200F", -- power up all 4 | |

| − | + | X"40FF", -- control mask 0xFF | |

| − | + | X"1000", -- range 0 on dac0 | |

| − | + | X"1101", -- range 1 on dac1 | |

| − | + | X"1202", -- range 2 on dac2 | |

| − | + | X"1303", -- range 3 on dac3 | |

| − | + | X"1004", -- range 4 on dac4 | |

| − | + | X"1105", -- range 5 on dac5 | |

| − | + | X"1202", -- range 2 on dac6 | |

| − | + | X"1303", -- range 3 on dac7 | |

| − | + | X"43FF", -- dac mask 0xFF | |

| − | + | X"0010", -- DAC0 | |

| − | + | X"0001", -- 1 | |

| − | + | X"0002", -- 2 | |

| − | + | X"0003", -- 3 | |

| − | + | X"0004", -- 4 | |

| − | + | X"0005", -- 5 | |

| − | + | X"0006", -- 6 | |

| − | + | X"0007", -- 7 | |

| − | + | X"8000", -- time interval 100 | |

| − | + | X"0064", | |

| − | + | X"410F", -- dac mask 0x0F | |

| − | + | X"0000", -- DAC0 | |

| + | X"0010", -- 1 | ||

| + | X"0020", -- 2 | ||

| + | X"0030", -- DAC3 | ||

| + | X"8000", -- time interval 50 | ||

| + | X"0032", | ||

| + | X"41F0", -- dac 0xF0 | ||

| + | X"1040", -- DAC4 | ||

| + | X"2050", -- 5 | ||

| + | X"3060", -- 6 | ||

| + | X"4070", -- DAC7 | ||

| + | X"8000", -- time interval 200 | ||

| + | X"00C8", | ||

| + | X"4105", -- dac mask 0x05 | ||

| + | X"2000", -- DAC0 | ||

| + | X"1020", -- DAC2 | ||

| + | X"FFFF", -- pause | ||

| + | X"FFFF", | ||

| + | X"8000", -- time interval 50 | ||

| + | X"0032", | ||

| + | X"41C0", -- dac mask 0xC0 | ||

| + | X"FFF6", -- DAC6 | ||

| + | X"1007", -- DAC7 | ||

| + | X"8000", -- stop | ||

| + | X"0000", | ||

There are two SPI interfaces, running in parallel: | There are two SPI interfaces, running in parallel: | ||

| Line 159: | Line 211: | ||

E.g. when using channels 1,2,4,7 the update speed will be higher than when using 0,1,2,3. | E.g. when using channels 1,2,4,7 the update speed will be higher than when using 0,1,2,3. | ||

| + | == DAC output register == | ||

| + | |||

| + | First set the mask like | ||

| + | 0x | ||

== DAC control register == | == DAC control register == | ||

| Line 174: | Line 230: | ||

command syntax: | command syntax: | ||

| − | Name register number | | + | Name register number | dac # | channel mask |

| − | Bits | + | Bits 14-12 | 10-8 | 3-0 |

Memory content | Memory content | ||

------------------- | ------------------- | ||

0x4011 // Set DAC control register command, mask = 0x11 one channel pro DAC chip | 0x4011 // Set DAC control register command, mask = 0x11 one channel pro DAC chip | ||

| − | + | b0010 X000 XXXX 1111 // Set DAC SPI register '010' channel mask '1111'= all channel 0-3 on | |

| − | + | b0010 X000 XXXX 1111 // Set DAC SPI register '010' channel mask '1111'= all channel 4-7 on | |

0x4011 // Set DAC control register command, mask = 0x11 one channel pro DAC chip | 0x4011 // Set DAC control register command, mask = 0x11 one channel pro DAC chip | ||

| − | + | b0010 X000 XXXX 1100 // Set DAC SPI register '010' channel mask '1100'= channel 2 and 3 on, 0 and 1 off | |

| − | + | b0010 X000 XXXX 0011 // Set DAC SPI register '010' channel mask '0011'= channel 4 and 5 on, 6 and 7 off | |

| Line 190: | Line 246: | ||

command syntax: | command syntax: | ||

| − | Name register number | | + | Name register number | dac # | output range |

| − | Bits | + | Bits 14-12 | 10-8 | 2-0 |

Memory content | Memory content | ||

---------------------- | ---------------------- | ||

0x403F // Set the first six DAC channels | 0x403F // Set the first six DAC channels | ||

| − | + | b0001 0000 XXXX X000 // 5V (channel 0) | |

| − | + | b0001 0001 XXXX X001 // 10V (channel 1) | |

| − | + | b0001 0011 XXXX X010 // 10.8V (channel 3) | |

| − | + | b0001 0010 XXXX X011 // +/-5V (channel 2) | |

| − | + | b0001 0000 XXXX X100 // +/-10V (channel 0) | |

| − | + | b0001 0001 XXXX X101 // +/-10.8 (channel 1) | |

| − | REG #DAC | + | REG #DAC VAL |

The Memory values are mapped to the SPI bits in the FPGA implementation: | The Memory values are mapped to the SPI bits in the FPGA implementation: | ||

| − | DACC[ | + | DACC[14..12] -> SPI_DATA[21..19] (Register number) |

| − | DACC[ | + | DACC[10.. 8] -> SPI_DATA[18..16] (DAC number 0..3) |

DACC[ 3.. 0] -> SPI_DATA[ 3.. 0] (data value, depends on register number) | DACC[ 3.. 0] -> SPI_DATA[ 3.. 0] (data value, depends on register number) | ||

| + | |||

| + | In Hex the control register is 0xRN0V : R-register#, N-DAC number, V-value of the register | ||

| + | |||

| + | The DAC number should be from 0 to 3!!! DAC# 4 is broadcast to all 4 DACs in the chip. DAC#4..7 on the board are actuall DAC#0..3 of the second chip. | ||

Most used DAC values (the default values are all 0) | Most used DAC values (the default values are all 0) | ||

Latest revision as of 14:32, 12 April 2018

Contents

Description

This module is a Digital to analog converter with 8 isolated channels and integrated RAM (4M x 16-bit) memory. It is populated with a tiny FPGA to generate voltage sequences.

Two DACs AD57X4 from Analog Devices were used, this family consist of three DACs with 12, 14 and 16-bit resolution. They can operate from single-supply voltages from +4.5 V up to +16.5 V or dual-supply voltages from ±4.5 V up to ±16.5 V. Nominal full-scaleoutput range is software-selectable from +5 V, +10 V, +10.8 V,±5 V, ±10 V, or ±10.8 V. The SU741 power supply will be customized for each application if you do not need to work with the maximal output range. The DAC uses a serial interface that operates at 30 MHz clock rates. Double buffering allows the simultaneous updating of all DACs channels.

Block Diagram

Front panel

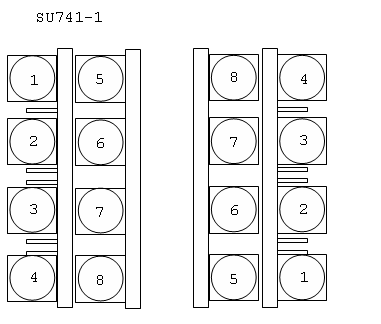

Back Connector

SU741 pin table (direction shown for the SU board!)

power in +5V 2 1 +5V in power

LVTTL bidir D<1> 4 3 D<0> bidir LVTTL

LVTTL bidir D<3> 6 5 D<2> bidir LVTTL

LVTTL bidir D<5> 8 7 D<4> bidir LVTTL

LVTTL bidir D<7> 10 9 D<6> bidir LVTTL

LVTTL bidir D<9> 12 11 D<8> bidir LVTTL

LVTTL bidir D<11> 14 13 D<10> bidir LVTTL

LVTTL bidir D<13> 16 15 D<12> bidir LVTTL

LVTTL bidir D<15> 18 17 D<14> bidir LVTTL

LVTTL in REQ 20 19 READ_n in LVTTL

LVTTL in Addr<1> 22 21 Addr<0> in LVTTL

LVTTL in CMD_n 24 23 Sync in LVTTL

LVTTL out READY 26 25 CLK in LVTTL

LVTTL in DAC 28 27 FCLR in LVTTL

* in LDACn 30 29 SPI_SDO_CLR out *

* in SPI_CLK 32 31 SPI_DIN2 in *

* in SPI_DIN1 34 33 SPI_Sync_n in *

power in GND 36 35 GND in power

- Note: when FCLR is 1, the DAC and SPI signals (pin29..pin34) can be driven from the LogicBox.

Otherwise the LogicBox should NOT drive these 6 signals! They are driven by the FPGA on SU741!

Differences to SU730 as till Feb 2014:

- the memory is 4M x 16 instead of 8M x 16 - there is a direct connection to the SPI and DAC interface - no HISTO and CRE signals on the SU-connector (CRE was anyway not used) - Addr2 is now Sync (10 MHz for time measurement), therefore 2 instead of 4 address pointers - DAC signal has another meaning (was anyway not used before) - control/command/status registers - still not fully defined and implemented, used for start/pause/stop and more.

Power consumption

+5V -> 150 mA

Measurement

Others

Interface:

req cmd_n iaddr1 iaddr0 read_n dac fclr Bits Name Comment x x x x x x 1 x - clear address counters and state machines, tri-state the SPI signals 1 0 N=0..1 0 1 0 0 16 AC0..1 write bits 15.. 0 of address counter N, AC[N][15..0]=DI 1 0 N=0..1 1 1 0 0 6 AC0..1 write bits 21..16 of address counter N, AC[N][21..16]=DI[5..0] 1 0 N=0..1 0 0 0 0 16 AC0..1 read lower part of address counter: DO=AC[N][15..0] 1 0 N=0..1 1 0 0 0 6 AC0..1 read upper part of address counter: DO[5..0]=AC[N][21..16] ---------------------------------------------------------- 1 0 N=0..3 1 1 0 16 CR0..3 write control/command register CR[N] 1 0 N=0..3 0 1 0 16 CR0..3 read control/command/status register CR[N] ---------------------------------------------------------- 1 1 N=0..1 0 1 0 0 16 memory write: mem[AC[N]]=DI 1 1 N=0..1 1 1 0 0 16 memory write with address increment: mem[AC[N]]=DI, AC[N]++ ---------------------------------------------------------- 1 1 N=0..1 0 0 0 0 16 memory read: DO=mem[AC[N]] 1 1 N=0..1 1 0 0 0 16 memory read with address increment: DO=mem[AC[N]], AC[N]++ ---------------------------------------------------------- ---------------------------------------------------------------------

DI are the data coming from the Logic Box DO are the data to the Logic Box

sync is a slow clock (10 MHz) for the time measurement

Bit positions writing to CR[3] : 0 : start from the beginning or continue, 1 : pause, 2 : continue, 3 : stop ... DI/DO 0..15 read_n 16 req 17 iaddr 18..19 sync 20 cmd_n 21 clk 22 ready 23 fclr 24 dac 25

Status register:

Read from CR[3]:

bits 2..0 : state machine communication with LogicBox with states: idle(0), latch_cmd(1), read_ac(2), write_ac(3), read_ram(4), write_ram(5), finish(6) bits 6..4 : state machine read/write to PSRAM with states: idle(0), read_a(1), read_d(2), read_l(3), write_a(4), write_d(5), finish(6) bits 11..8 : state machine of the sequencer with states: idle(0), sent_ram_rq(1), read_tmH(2), read_tmL(3), read_dvH(4), read_dvL(5), read_dac_dmc(6), check_mask(7), read_dac(8), ldac_soft(9), st_pause(10), wait_dt(11), check_for_pause_stop(12)

How to operate:

1) init both address pointers with the same (either with fclr or by writing to AC[0] and AC[1])

2) write the memory content with address autoincrement using e.g. AC[1]

3) start the sequency by writing 0 to the CR[3]

4) later reading status from CR is allowed, but memory read/write is blocked while running the sequence

RAM information

Bits

15 14 0 Comment

1 < time_step[30..16] > 31-bit time step to the next DAC update

< time_step[15.. 0] > Special words:

0xFFFF FFFF - pause,

0x8000 0000 - stop

0xFFFF FFFE - send immediately

0 0 < divider[29..16] > Program divider for the time_step

< divider[15.. 0] >

0 1 < command[5..0]> < ADCmask[7..0] > command = 0 : DAC config register, no LDAC generated (not necessary)

command = 1 : DAC output register, generate LDAC at the end of the current time interval

command = 3 : DAC output register, generate LDAC immediately

< DAC output LSB non-zero bit in mask >

...

< DAC output MSB non-zero bit in mask >

Example:

Data Comment X"0000", -- div ratio 1 X"0001", X"4011", -- control mask 0x11 X"200F", -- power up all 4 X"200F", -- power up all 4 X"40FF", -- control mask 0xFF X"1000", -- range 0 on dac0 X"1101", -- range 1 on dac1 X"1202", -- range 2 on dac2 X"1303", -- range 3 on dac3 X"1004", -- range 4 on dac4 X"1105", -- range 5 on dac5 X"1202", -- range 2 on dac6 X"1303", -- range 3 on dac7 X"43FF", -- dac mask 0xFF X"0010", -- DAC0 X"0001", -- 1 X"0002", -- 2 X"0003", -- 3 X"0004", -- 4 X"0005", -- 5 X"0006", -- 6 X"0007", -- 7 X"8000", -- time interval 100 X"0064", X"410F", -- dac mask 0x0F X"0000", -- DAC0 X"0010", -- 1 X"0020", -- 2 X"0030", -- DAC3 X"8000", -- time interval 50 X"0032", X"41F0", -- dac 0xF0 X"1040", -- DAC4 X"2050", -- 5 X"3060", -- 6 X"4070", -- DAC7 X"8000", -- time interval 200 X"00C8", X"4105", -- dac mask 0x05 X"2000", -- DAC0 X"1020", -- DAC2 X"FFFF", -- pause X"FFFF", X"8000", -- time interval 50 X"0032", X"41C0", -- dac mask 0xC0 X"FFF6", -- DAC6 X"1007", -- DAC7 X"8000", -- stop X"0000",

There are two SPI interfaces, running in parallel: Group 0: DAC channels 0..3 Group 1: DAC channels 4..7

For highest update speed distribute the used channels equally in the two groups.

E.g. when using channels 1,2,4,7 the update speed will be higher than when using 0,1,2,3.

DAC output register

First set the mask like

0x

DAC control register

to set the control register of the dac, the memory must have the word 0x40FF

The High byte specify the command "Set DAC control register" (0x40). The Low byte specify the channels to be set, is a mask(0xFF all channels).

If all DAC channel are to be set 8x16-Bits words must be written in memory , with the control register information for each DAC channel. If only 3 channels are to be set 3x16-Bits words must be written in memory , with the control register information for each DAC channel. The command to switch on/off the channels is an exception. All channels can be activated/deactivated only with two 3 16-Bits words. See example:

Example 1: Enable channels command syntax: Name register number | dac # | channel mask Bits 14-12 | 10-8 | 3-0 Memory content ------------------- 0x4011 // Set DAC control register command, mask = 0x11 one channel pro DAC chip b0010 X000 XXXX 1111 // Set DAC SPI register '010' channel mask '1111'= all channel 0-3 on b0010 X000 XXXX 1111 // Set DAC SPI register '010' channel mask '1111'= all channel 4-7 on 0x4011 // Set DAC control register command, mask = 0x11 one channel pro DAC chip b0010 X000 XXXX 1100 // Set DAC SPI register '010' channel mask '1100'= channel 2 and 3 on, 0 and 1 off b0010 X000 XXXX 0011 // Set DAC SPI register '010' channel mask '0011'= channel 4 and 5 on, 6 and 7 off

Example 2: Setting channel input range to different values command syntax: Name register number | dac # | output range Bits 14-12 | 10-8 | 2-0 Memory content ---------------------- 0x403F // Set the first six DAC channels b0001 0000 XXXX X000 // 5V (channel 0) b0001 0001 XXXX X001 // 10V (channel 1) b0001 0011 XXXX X010 // 10.8V (channel 3) b0001 0010 XXXX X011 // +/-5V (channel 2) b0001 0000 XXXX X100 // +/-10V (channel 0) b0001 0001 XXXX X101 // +/-10.8 (channel 1) REG #DAC VAL

The Memory values are mapped to the SPI bits in the FPGA implementation:

DACC[14..12] -> SPI_DATA[21..19] (Register number) DACC[10.. 8] -> SPI_DATA[18..16] (DAC number 0..3) DACC[ 3.. 0] -> SPI_DATA[ 3.. 0] (data value, depends on register number)

In Hex the control register is 0xRN0V : R-register#, N-DAC number, V-value of the register

The DAC number should be from 0 to 3!!! DAC# 4 is broadcast to all 4 DACs in the chip. DAC#4..7 on the board are actuall DAC#0..3 of the second chip.

Most used DAC values (the default values are all 0)

R/nW Z REG A DATA

23 22 21..19 18..16 15..0

0 0 0 0 0 dac# value : set dac# value, for 14 bit DAC the two LSBs are don't care, for 12 bit DAC the 4 LSBs are don't care.

0 0 0 0 1 dac# range : set output range of dac#, 0 1 2 3 4 5

: 5V 10V 10.8V +/-5V +/-10V +/-10.8

0 0 0 1 0 0 0 0 power : set bits 0..3 to power up DAC 0..3 (default is off and this reg must be set)

0 0 0 1 1 0 0 0 - : NOP (= 0x18XXXX)

0 0 0 1 1 0 0 1 control : Bit 3 is TSD (thermal shutdown enable), Bit 2 is current-limit clamp enable

: Bit 1 is Clear select 0: clear to 0V, 1: clear to midscale (unipolar) or negative full scale (bipolar)

: Bit 0 is SDO disable

0 0 0 1 1 1 0 0 - : clear, update the DAC register with the clear code and set the outputs

0 0 0 1 1 1 0 1 - : load, update the DAC register and set the outputs