Difference between revisions of "SU706"

(→Compatibility) |

(→Back Connector) |

||

| Line 15: | Line 15: | ||

= Back Connector = | = Back Connector = | ||

| − | == Version | + | == Version 1 == |

| − | + | SU706 pin table (direction shown for the SU board!) | |

| + | power in +5V 2 1 +5V in power | ||

| + | LVTTL in RESET 4 3 CLKout out LVTTL | ||

| + | LVTTL out DATA<0> 6 5 DATA<1> out LVTTL | ||

| + | LVTTL out DATA<2> 8 7 DATA<3> out LVTTL | ||

| + | LVTTL out DATA<4> 10 9 DATA<5> out LVTTL | ||

| + | LVTTL out DATA<6> 12 11 DATA<7> out LVTTL | ||

| + | LVTTL out DATA<8> 14 13 DATA<9> out LVTTL | ||

| + | LVTTL out DATA<10> 16 15 DATA<11> out LVTTL | ||

| + | LVTTL out DATA<12> 18 17 DATA<13> out LVTTL | ||

| + | NC - - 20 19 SCLKn in LVTTL | ||

| + | LVTTL in SDATA 22 21 SEn in LVTTL | ||

| + | LVTTL in CLKp 24 23 DIO1OUT in LVTTL | ||

| + | LVTTL in DIO2OUT 26 25 DIO2OEn in LVTTL | ||

| + | LVTTL in DIO1OEn 28 27 DIO2IN out LVTTL | ||

| + | NC - - 30 29 DIO1IN out LVTTL | ||

| + | NC - - 32 31 CLKn in LVTTL | ||

| + | NC - - 34 33 - - NC | ||

| + | power in GND 36 35 GND in power | ||

| + | |||

| + | == Version 2 == | ||

power in +5V 2 1 +5V in power | power in +5V 2 1 +5V in power | ||

| − | + | LVTTL in RESET 4 3 CLKout out LVTTL | |

| − | + | LVTTL out DATA<0> 6 5 DATA<1> out LVTTL | |

| − | + | LVTTL out DATA<2> 8 7 DATA<3> out LVTTL | |

| − | + | LVTTL out DATA<4> 10 9 DATA<5> out LVTTL | |

| − | + | LVTTL out DATA<6> 12 11 DATA<7> out LVTTL | |

| − | + | LVTTL out DATA<8> 14 13 DATA<9> out LVTTL | |

| − | + | LVTTL out DATA<10> 16 15 DATA<11> out LVTTL | |

| − | + | LVTTL out DATA<12> 18 17 DATA<13> out LVTTL | |

| − | + | LVTTL out OVR 20 19 SCLKn in LVTTL | |

| − | LVTTL | + | LVTTL in SDATA 22 21 SEn in LVTTL |

| − | LVTTL in | + | LVTTL in CLKn 24 23 CLKp in LVTTL |

| − | LVTTL in | + | LVTTL in DIO2OUT 26 25 DIO2OEn in LVTTL |

| − | LVTTL in | + | LVTTL in DIO1OEn 28 27 DIO2IN out LVTTL |

| − | + | LVTTL in DIO1OUT 30 29 DIO1IN out LVTTL | |

| − | + | LVTTL in LED1n 32 31 LED2n in LVTTL | |

NC - - 34 33 - - NC | NC - - 34 33 - - NC | ||

power in GND 36 35 GND in power | power in GND 36 35 GND in power | ||

Revision as of 13:55, 12 September 2014

Contents

Description

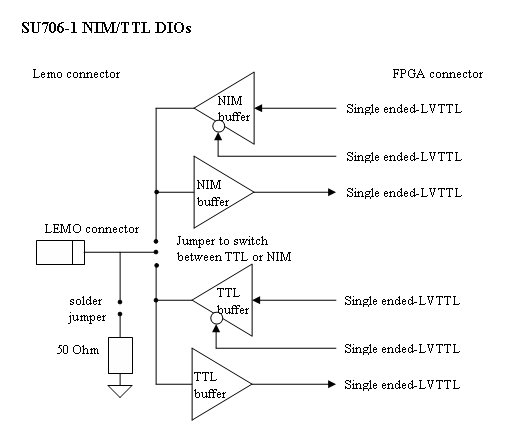

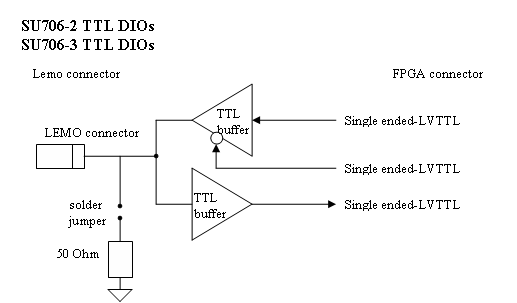

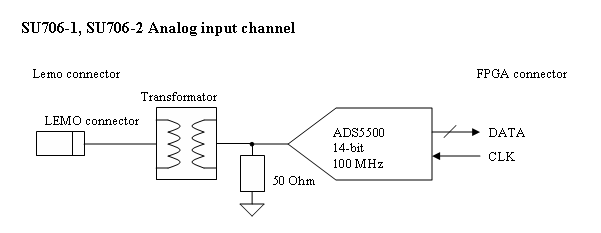

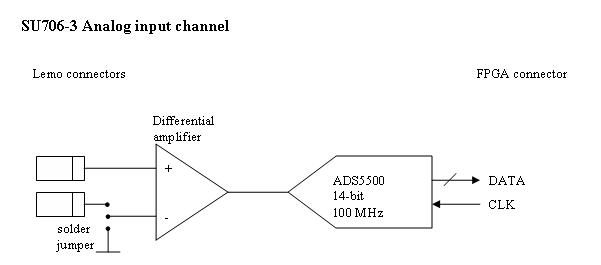

Block Diagram

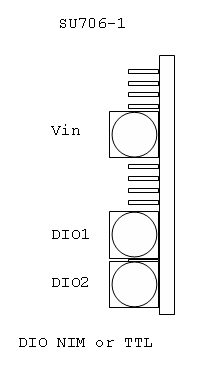

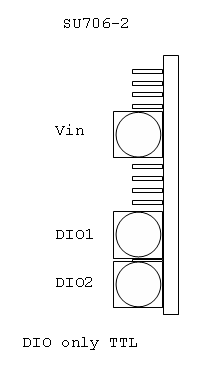

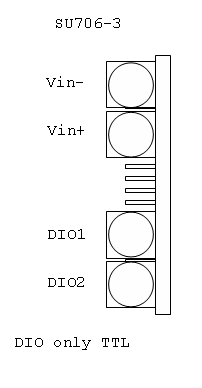

Front panel

Back Connector

Version 1

SU706 pin table (direction shown for the SU board!)

power in +5V 2 1 +5V in power

LVTTL in RESET 4 3 CLKout out LVTTL

LVTTL out DATA<0> 6 5 DATA<1> out LVTTL

LVTTL out DATA<2> 8 7 DATA<3> out LVTTL

LVTTL out DATA<4> 10 9 DATA<5> out LVTTL

LVTTL out DATA<6> 12 11 DATA<7> out LVTTL

LVTTL out DATA<8> 14 13 DATA<9> out LVTTL

LVTTL out DATA<10> 16 15 DATA<11> out LVTTL

LVTTL out DATA<12> 18 17 DATA<13> out LVTTL

NC - - 20 19 SCLKn in LVTTL

LVTTL in SDATA 22 21 SEn in LVTTL

LVTTL in CLKp 24 23 DIO1OUT in LVTTL

LVTTL in DIO2OUT 26 25 DIO2OEn in LVTTL

LVTTL in DIO1OEn 28 27 DIO2IN out LVTTL

NC - - 30 29 DIO1IN out LVTTL

NC - - 32 31 CLKn in LVTTL

NC - - 34 33 - - NC

power in GND 36 35 GND in power

Version 2

power in +5V 2 1 +5V in power

LVTTL in RESET 4 3 CLKout out LVTTL

LVTTL out DATA<0> 6 5 DATA<1> out LVTTL

LVTTL out DATA<2> 8 7 DATA<3> out LVTTL

LVTTL out DATA<4> 10 9 DATA<5> out LVTTL

LVTTL out DATA<6> 12 11 DATA<7> out LVTTL

LVTTL out DATA<8> 14 13 DATA<9> out LVTTL

LVTTL out DATA<10> 16 15 DATA<11> out LVTTL

LVTTL out DATA<12> 18 17 DATA<13> out LVTTL

LVTTL out OVR 20 19 SCLKn in LVTTL

LVTTL in SDATA 22 21 SEn in LVTTL

LVTTL in CLKn 24 23 CLKp in LVTTL

LVTTL in DIO2OUT 26 25 DIO2OEn in LVTTL

LVTTL in DIO1OEn 28 27 DIO2IN out LVTTL

LVTTL in DIO1OUT 30 29 DIO1IN out LVTTL

LVTTL in LED1n 32 31 LED2n in LVTTL

NC - - 34 33 - - NC

power in GND 36 35 GND in power

Power consumption

Version 0

+5V -> XX mA -5V -> XX mA

Measurement

Version 0

Compatibility

This module is compatible with all base boards