Difference between revisions of "SU707"

(→Version 2 (and version 1)) |

|||

| (19 intermediate revisions by the same user not shown) | |||

| Line 2: | Line 2: | ||

| − | This module family consists of 8 LVDS digital input output (DIO). As connector is used two RJ45, so the user can use a standard patch cable to send/receive information. We recommended to use a cat5e cable or superior. This DIOs can be used to transmit a clock or signals in noisy environments. | + | This module family consists of 8 LVDS digital input output (DIO). As connector is used two RJ45, so the user can use a standard patch cable to send/receive information. We recommended to use a cat5e cable or superior. This DIOs can be used to transmit a clock or signals in noisy environments. '''The version 0 should not be used!, the differential pair are not compatible with the standard patch cable.''' |

| + | This information applies only to version 1 and 2: | ||

| − | == Version 0 == | + | If you want to use as input a DIO, you should populate a 110 Ohm resistor, this resistors are in the board at the parking resistor lot. You have to set the DIO always in groups of two. If you set the DIO1 as input the DIO2 must be an input and so on, see block diagram for more information. |

| + | |||

| + | == Version 0 (do not use this version!)== | ||

This version has to group of 4 channels, you can populat each group as input or output. If the transceiver and receiver of one group are populated, you can dynamically set up the group as input or output, but the driver will use only the half voltage. | This version has to group of 4 channels, you can populat each group as input or output. If the transceiver and receiver of one group are populated, you can dynamically set up the group as input or output, but the driver will use only the half voltage. | ||

| Line 12: | Line 15: | ||

receiver ic: SN75LVDS390PW, speed up to 200 Mbps, detects 100mV (for more details see datasheet) | receiver ic: SN75LVDS390PW, speed up to 200 Mbps, detects 100mV (for more details see datasheet) | ||

| − | == Version 2 (and version 1) == | + | == Version 2 (and version 1 do not use this version!) == |

| − | The version 1 will not be produced any more, the | + | The version 1 will not be produced any more, the differences with the version 2 are that the version 1 is not pin compatible with the base board DL701 and DL706, due the use of the pin 34 of the back connector. The version 2 is compatible with all base boards. |

| − | + | These versions has three main difference respect the version 0. The first one is that now the 110 Ohm resistor needed to use a DIO as input is external. The user has to put it in from the resistors parking lot. The second one is that now there is 4 groups of two DIO. The last one is that you can populate an oscillator which is connected to the DIO number 5. | |

The following integrated circuits are used in this board: | The following integrated circuits are used in this board: | ||

| − | |||

| − | SN75LVDS390D | + | sender ic : SN75LVDS391D, speed up to 200 Mbps, typical output voltage 350 mV @ 100 Ohm load (for more details see datasheet) |

| + | |||

| + | receiver ic: SN75LVDS390D, speed up to 200 Mbps, detects 100mV (for more details see datasheet) | ||

= Block Diagram = | = Block Diagram = | ||

| Line 28: | Line 32: | ||

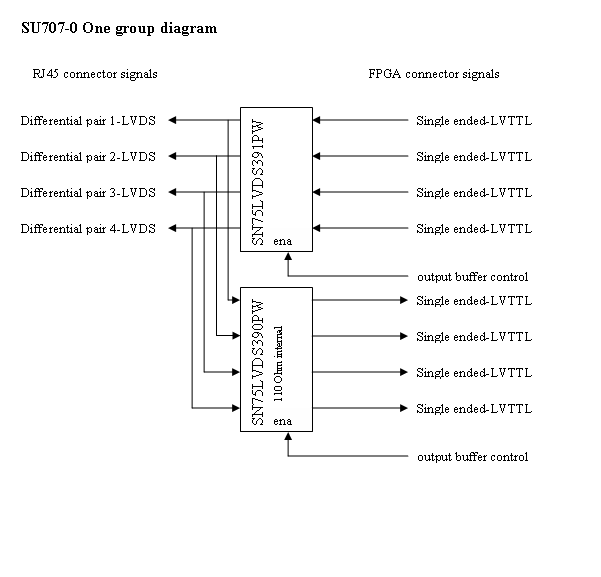

== Version 0 == | == Version 0 == | ||

| + | [[File:SU707-0_block_diagram.png]] | ||

| + | |||

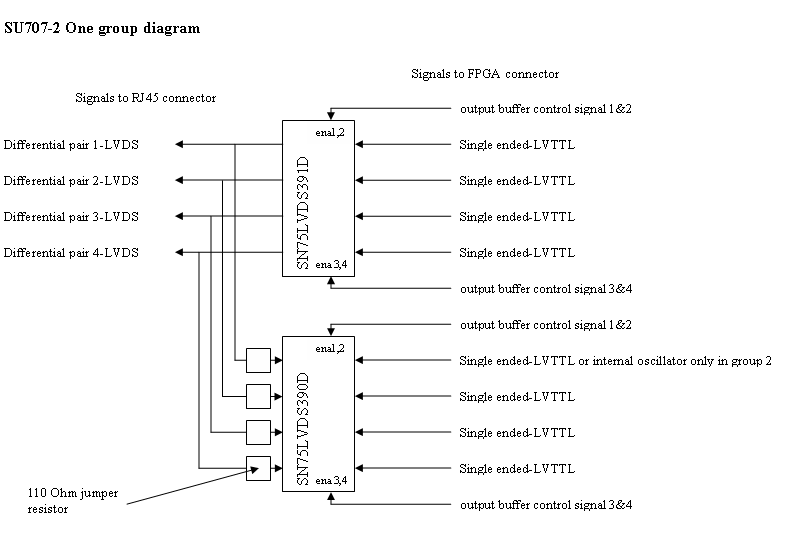

| + | == Version 1,2 == | ||

| + | [[File:SU707-2_block_diagram.png]] | ||

= Front panel = | = Front panel = | ||

| Line 34: | Line 42: | ||

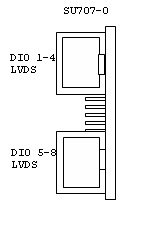

== Version 0 == | == Version 0 == | ||

| − | + | [[File:SU707-0_Front_panel.png]] | |

| − | + | ||

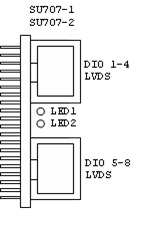

| − | + | == Version 1,2 == | |

| − | + | ||

| − | + | [[File:SU707-2_front_panel.png]] | |

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

= Back Connector = | = Back Connector = | ||

| Line 139: | Line 129: | ||

= Compatibility = | = Compatibility = | ||

| − | + | '''You should use only the version 2 of this board!'''. The version 0 and 2 is compatible with all base boards. The version 1 is not compatible with the DL701 and DL706 base board. | |

| + | |||

| + | |||

| + | {{:Digital input/output (DIO)}} | ||

Latest revision as of 22:11, 19 September 2014

Contents

Description

This module family consists of 8 LVDS digital input output (DIO). As connector is used two RJ45, so the user can use a standard patch cable to send/receive information. We recommended to use a cat5e cable or superior. This DIOs can be used to transmit a clock or signals in noisy environments. The version 0 should not be used!, the differential pair are not compatible with the standard patch cable. This information applies only to version 1 and 2:

If you want to use as input a DIO, you should populate a 110 Ohm resistor, this resistors are in the board at the parking resistor lot. You have to set the DIO always in groups of two. If you set the DIO1 as input the DIO2 must be an input and so on, see block diagram for more information.

Version 0 (do not use this version!)

This version has to group of 4 channels, you can populat each group as input or output. If the transceiver and receiver of one group are populated, you can dynamically set up the group as input or output, but the driver will use only the half voltage.

sender ic : SN75LVDS391PW, speed up to 200 Mbps, typical output voltage 350 mV @ 100 Ohm load (for more details see datasheet)

receiver ic: SN75LVDS390PW, speed up to 200 Mbps, detects 100mV (for more details see datasheet)

Version 2 (and version 1 do not use this version!)

The version 1 will not be produced any more, the differences with the version 2 are that the version 1 is not pin compatible with the base board DL701 and DL706, due the use of the pin 34 of the back connector. The version 2 is compatible with all base boards.

These versions has three main difference respect the version 0. The first one is that now the 110 Ohm resistor needed to use a DIO as input is external. The user has to put it in from the resistors parking lot. The second one is that now there is 4 groups of two DIO. The last one is that you can populate an oscillator which is connected to the DIO number 5.

The following integrated circuits are used in this board:

sender ic : SN75LVDS391D, speed up to 200 Mbps, typical output voltage 350 mV @ 100 Ohm load (for more details see datasheet)

receiver ic: SN75LVDS390D, speed up to 200 Mbps, detects 100mV (for more details see datasheet)

Block Diagram

Version 0

Version 1,2

Front panel

Version 0

Version 1,2

Back Connector

Version 0

SU707 pin table (direction shown for the SU board!)

power in +5V 2 1 +5V in power

LVTTL out LVDS_I<1> 4 3 LVDS_I<2> out LVTTL

LVTTL in LVDS_O<1> 6 5 LVDS_O<2> in LVTTL

LVTTL in LVDS_O<3> 8 7 LVDS_O<4> in LVTTL

LVTTL out LVDS_I<3> 10 9 LVDS_I<4> out LVTTL

LVTTL out LVDS_I<5> 12 11 LVDS_I<6> out LVTTL

LVTTL in LVDS_O<5> 14 13 LVDS_O<6> in LVTTL

LVTTL in LVDS_O<7> 16 15 LVDS_O<8> in LVTTL

LVTTL out LVDS_I<7> 18 17 LVDS_I<8> out LVTTL

LVTTL in EN_O<2> 20 19 EN_I<2> in LVTTL

LVTTL in EN_O<1> 22 21 EN_I<1> in LVTTL

NC - - 24 23 - - NC

NC - - 26 25 - - NC

NC - - 28 27 - - NC

NC - - 30 29 - - NC

NC - - 32 31 - - NC

NC - - 34 33 - - NC

power in GND 36 35 GND in power

Version 1

power in +5V 2 1 +5V in power LVTTL in LVDS_O<1> 4 3 EN_O<1> in LVTTL LVTTL in LVDS_O<2> 6 5 EN_O<2> in LVTTL LVTTL in LVDS_O<3> 8 7 - - NC LVTTL in LVDS_O<4> 10 9 - - NC LVTTL out LVDS_I<1> 12 11 EN_I<1> in LVTTL LVTTL out LVDS_I<2> 14 13 EN_I<2> in LVTTL LVTTL out LVDS_I<3> 16 15 LED<1> in LVTTL LVTTL out LVDS_I<4> 18 17 LED<2> in LVTTL LVTTL in LVDS_O<5> 20 19 EN_O<3> in LVTTL LVTTL in LVDS_O<6> 22 21 EN_O<4> in LVTTL LVTTL in LVDS_O<7> 24 23 - - NC LVTTL in LVDS_O<8> 26 25 - - NC LVTTL out LVDS_I<5> 28 27 EN_I<3> in LVTTL LVTTL out LVDS_I<6> 30 29 EN_I<4> in LVTTL LVTTL out LVDS_I<7> 32 31 - - NC LVTTL out LVDS_I<8> 34 33 - - NC power in GND 36 35 GND in power

Version 2

power in +5V 2 1 +5V in power

LVTTL in LVDS_O<1> 4 3 EN_O<1> in LVTTL

LVTTL in LVDS_O<2> 6 5 EN_O<2> in LVTTL

LVTTL in LVDS_O<3> 8 7 - - NC

LVTTL in LVDS_O<4> 10 9 - - NC

LVTTL out LVDS_I<1> 12 11 EN_I<1> in LVTTL

LVTTL out LVDS_I<2> 14 13 EN_I<2> in LVTTL

LVTTL out LVDS_I<3> 16 15 LED<1> in LVTTL

LVTTL out LVDS_I<4> 18 17 LED<2> in LVTTL

LVTTL in LVDS_O<5> 20 19 EN_O<3> in LVTTL

LVTTL in LVDS_O<6> 22 21 EN_O<4> in LVTTL

LVTTL in LVDS_O<7> 24 23 - - NC

LVTTL in LVDS_O<8> 26 25 - - NC

LVTTL out LVDS_I<5> 28 27 EN_I<3> in LVTTL

LVTTL out LVDS_I<6> 30 29 EN_I<4> in LVTTL

LVTTL out LVDS_I<7> 32 31 LVDS_I<8> out LVDS

NC - - 34 33 - - NC

power in GND 36 35 GND in power

Power consumption

Version 0

+5V -> XX mA -5V -> XX mA

Measurement

Version 0

Compatibility

You should use only the version 2 of this board!. The version 0 and 2 is compatible with all base boards. The version 1 is not compatible with the DL701 and DL706 base board.

LogicPool (DIO)

This module supports several hardware expansions cards or submodules, no all functionalities are supported for all submodules.

Models

There is only one model for this module.

Supported hardware

SU700, SU701, SU703, SU704, SU706, SU707

Register Map

Module Address: 'T' or Ox54

Read register

| Register Address | Name | Data |

|---|---|---|

| 0 | MUX_IN | Bit 7..0: multiplexer address |

| 1 | STATE_IN | Bit 7..0: input value |

Write register

| Register Address | Name | Data |

|---|---|---|

| 0 | MUX_OUT | Bit 7..0: multiplexer address |

| 1 | Debounce | Bit 7..0: input value |

| 2 | Mode | Bit 0:

'1' 50 Ohm termination '0' Open Bit 1: NIM/TTL '1' NIM '0' TTL |

LabVIEW Vi

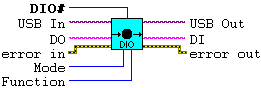

Digital Input/Output.

Support: SU700, SU701, SU703, SU704, SU706, SU707

According to hardware this supports either TTL,, TTL_coax, NIM or DIFFERENTIAL I/Os.

Each connector can be used as either an output (DO) or input (DI) or both.

If used as an input, terminal DO (driving output) must not be connected, as this enables the output driver and would override any input signals.

Please obey termination rules as defined for the specific used hardware!

The meaning of almost inputs and outputs of this Vi depends on the input "Function". The global inputs and outputs does not depend on the "function" input.

Glogal Inputs

DIO#: number of digital input/output to be accesed (1..255).

USB In: Handle to the LogicBox (create by open.vi), if not connected will take a global. parameter, this only works with one LogicBox at a time.

error in: error handling input

Global Outputs

USB out: Handle to the LogicBox.

error out: error handling output

Functions

Connect: connects all in/outputs and sets all parameters

Inputs:

"Mode": select the DIO standar.

"DO" : set the signal number which will drive the output, this signal can be set or clear

manually using the module "B_S.vi" (Bool to Signal).

"DI" : get the signal number of which drives this input.

Set DO: set the signal number which will drive the output, this signal can be set or clear manually

using the module "B_S.vi" (Bool to Signal).

input: "DO" : signal number or value.

Get DI: return the logic value of this input.

input: "DI": Logic value of this input.

Write Mode: Set the mode of the DIO.

input: "Mode" : TTL/LVDS

TTL 50 Ohm

NIM Open

NIM 50 Ohm

Example VIs

SU_DIO_Test.vi

or for a specific extension board:

SU700 -> SU700_TTLIO_Test.vi

SU707 -> SU707_Test.vi