Difference between revisions of "SU735"

(→Block Diagram) |

(→Compatibility) |

||

| (9 intermediate revisions by the same user not shown) | |||

| Line 4: | Line 4: | ||

This module can be used as Analog to digital converter or as charge to digital converter, it is a hardware option, you have to remove/populate some components. | This module can be used as Analog to digital converter or as charge to digital converter, it is a hardware option, you have to remove/populate some components. | ||

| − | As analog to digital converter, you can configure it to work with single ended or differential input signals, that is a hardware option too. As ADC was used the LTC225X or LTC226X family from linear technology | + | As analog to digital converter, you can configure it to work with single ended or differential input signals, that is a hardware option too. The maximal input voltage can be set to 1Vpp or 2Vpp, this can be set through a solder jumper. As ADC was used the LTC225X or LTC226X family from linear technology, see folowing table: |

{| border="1" class="wikitable" | {| border="1" class="wikitable" | ||

| Line 72: | Line 72: | ||

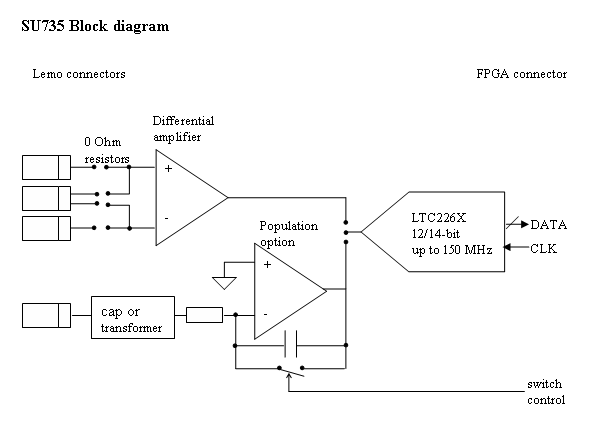

= Block Diagram = | = Block Diagram = | ||

| − | [[File: | + | [[File:SU735_block_diagram.png]] |

| − | + | = Front planel = | |

| + | |||

| + | == Version 0 == | ||

| − | + | [[File:SU735-0_Front_panel.png]] | |

| − | == Version | + | == Version 1,2 == |

| − | + | [[File:SU735-1_2_Front_panel.png]] | |

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

= Back Connector = | = Back Connector = | ||

| Line 184: | Line 155: | ||

LVTTL in CLKp 34 33 CLKn in LVTTL | LVTTL in CLKp 34 33 CLKn in LVTTL | ||

power in GND 36 35 GND in power | power in GND 36 35 GND in power | ||

| + | |||

| + | = Power consumption = | ||

| + | |||

| + | +5V -> 200 mA | ||

| + | |||

| + | -6V -> 75 mA | ||

| + | |||

| + | = Compatibility = | ||

| + | |||

| + | The Version 1 is compatible with all base boards. Versions 0 and 2 is only compatible with DL709, DL710 and DL711. DL701 and DL706 are not supported! | ||

= Others = | = Others = | ||

Latest revision as of 16:06, 10 November 2014

Contents

Description

This module can be used as Analog to digital converter or as charge to digital converter, it is a hardware option, you have to remove/populate some components.

As analog to digital converter, you can configure it to work with single ended or differential input signals, that is a hardware option too. The maximal input voltage can be set to 1Vpp or 2Vpp, this can be set through a solder jumper. As ADC was used the LTC225X or LTC226X family from linear technology, see folowing table:

| Type | Resolution | Sample rate |

|---|---|---|

| LTC2256-12 | 12-Bit | 25Msps |

| LTC2256-14 | 14-Bit | 25Msps |

| LTC2257-12 | 12-Bit | 40Msps |

| LTC2257-14 | 14-Bit | 40Msps |

| LTC2258-12 | 12-Bit | 65Msps |

| LTC2258-14 | 14-Bit | 65Msps |

| LTC2259-12 | 12-Bit | 80Msps |

| LTC2259-14 | 14-Bit | 80Msps |

| LTC2260-12 | 12-Bit | 105Msps |

| LTC2260-14 | 14-Bit | 105Msps |

| LTC2261-12 | 12-Bit | 125Msps |

| LTC2261-14 | 14-Bit | 125Msps |

| LTC2262-12 | 12-Bit | 150Msps |

| LTC2262-14 | 14-Bit | 150Msps |

Block Diagram

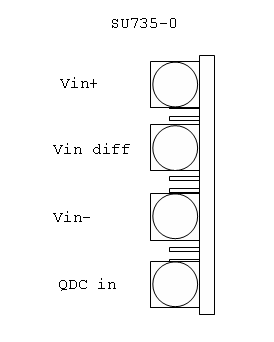

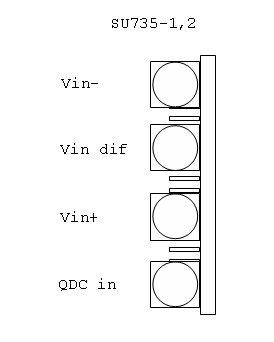

Front planel

Version 0

Version 1,2

Back Connector

Version 0 (first version no clock cleaner)

SU735 pin table (direction shown for the SU board!)

prototype

power in +5V 2 1 +5V in power

LVTTL in CLKp 4 3 CLKn in LVTTL

NC - - 6 5 - - NC

LVTTL out DATA<1> 8 7 DATA<0> out LVTTL

LVTTL out DATA<3> 10 9 DATA<2> out LVTTL

LVTTL out DATA<5> 12 11 DATA<4> out LVTTL

LVTTL out DATA<7> 14 13 DATA<6> out LVTTL

LVTTL out DATA<9> 16 15 DATA<8> out LVTTL

LVTTL out DATA<11> 18 17 DATA<10> out LVTTL

LVTTL out DATA<13> 20 19 DATA<12> out LVTTL

LVTTL in SPARE<1> 22 21 SPARE<0> in LVTTL

LVTTL in SPARE<3> 24 23 SPARE<2> in LVTTL

LVTTL in SPARE<5> 26 25 SPARE<4> in LVTTL

LVTTL in RESET 28 27 SPARE<6> in LVTTL

LVTTL in SCL 30 29 SDA bidir LVTTL

LVTTL out SDRD 32 31 SEn in LVTTL

LVTTL in SDATA 34 33 SCLKn in LVTTL

power in GND 36 35 GND in power

Version 1 (test version)

power in +5V 2 1 +5V in power LVTTL bidir SDA 4 3 SCL in LVTTL LVTTL out DATA<1> 6 5 DATA<0> out LVTTL LVTTL out DATA<3> 8 7 DATA<2> out LVTTL LVTTL out DATA<5> 10 9 DATA<4> out LVTTL LVTTL out DATA<7> 12 11 DATA<6> out LVTTL LVTTL out DATA<9> 14 13 DATA<8> out LVTTL LVTTL out DATA<11> 16 15 DATA<10> out LVTTL LVTTL out DATA<13> 18 17 DATA<12> out LVTTL LVTTL in SPARE<1> 20 19 GI_GATE in LVTTL LVTTL in SPARE<3> 22 21 SPARE<2> in LVTTL LVTTL in FREQ<1> 24 23 FREQ<0> in LVTTL LVTTL in RESET 26 25 CLK_CPU in LVTTL LVTTL out SDRD 28 27 SEn in LVTTL LVTTL in SCLKn 30 29 SDATA in LVTTL LVTTL in CLKp 32 31 CLKn in LVTTL NC - - 34 33 - - NC power in GND 36 35 GND in power

Version 2 (better layout)

production version

power in +5V 2 1 +5V in power

LVTTL bidir SDA 4 3 SCL in LVTTL

LVTTL out DATA<1> 6 5 DATA<0> out LVTTL

LVTTL out DATA<3> 8 7 DATA<2> out LVTTL

LVTTL out DATA<5> 10 9 DATA<4> out LVTTL

LVTTL out DATA<7> 12 11 DATA<6> out LVTTL

LVTTL out DATA<9> 14 13 DATA<8> out LVTTL

LVTTL out DATA<11> 16 15 DATA<10> out LVTTL

LVTTL out DATA<13> 18 17 DATA<12> out LVTTL

LVTTL in SPARE<1> 20 19 GI_GATE in LVTTL

LVTTL in SPARE<3> 22 21 SPARE<2> in LVTTL

LVTTL in FREQ<1> 24 23 FREQ<0> in LVTTL

LVTTL in RESET 26 25 CLK_CPU in LVTTL

LVTTL out SDRD 28 27 SEn in LVTTL

LVTTL in SCLKn 30 29 SDATA in LVTTL

NC - - 32 31 - - NC

LVTTL in CLKp 34 33 CLKn in LVTTL

power in GND 36 35 GND in power

Power consumption

+5V -> 200 mA

-6V -> 75 mA

Compatibility

The Version 1 is compatible with all base boards. Versions 0 and 2 is only compatible with DL709, DL710 and DL711. DL701 and DL706 are not supported!

Others

Ab SVN Version 25 CLK_CPU wird nicht mehr benötigt, es wird ein interner Oscillator benutzt. Jede Änderung der 2 Bits Freq<1:0> oder ein RESET Pulse startet die Initialisierung des Clock-Cleaner ICs.

Modifikation für R. Schicker: 2 digitalle Ausgänge auf den LEMOs J2 und J3 (U5 und viele Widerstände müsen weg).

Spare<1> und Spare<2> werden zu den 2 LEMOs durch das Lattice FPGA weitergeleitet.

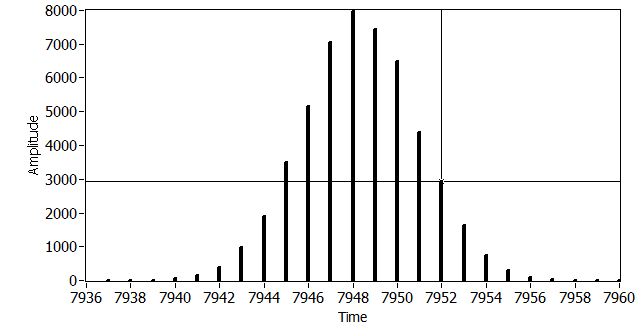

Measurement

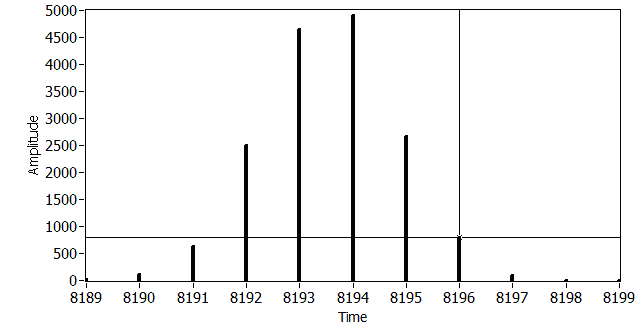

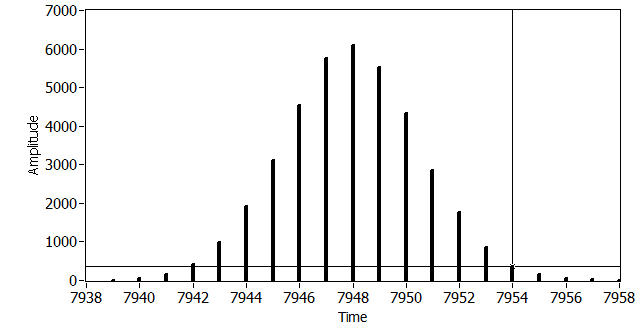

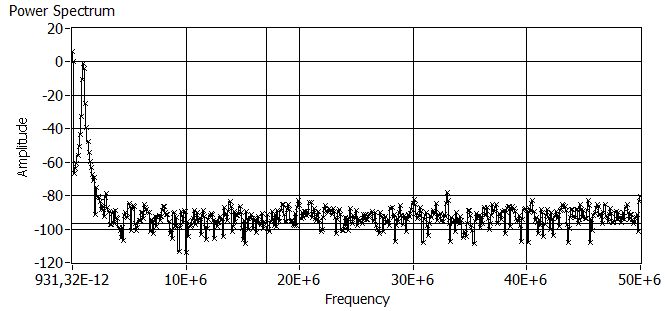

Board: LTC evaluation board. mean: 8193,55 variance: 1,58 std. deviation: 1,26 input: no signal samples: 16384 file: F:\SU735_14Bit_ADC\SU735-1\Entwicklung\Messungen\Ohne Signal.adc

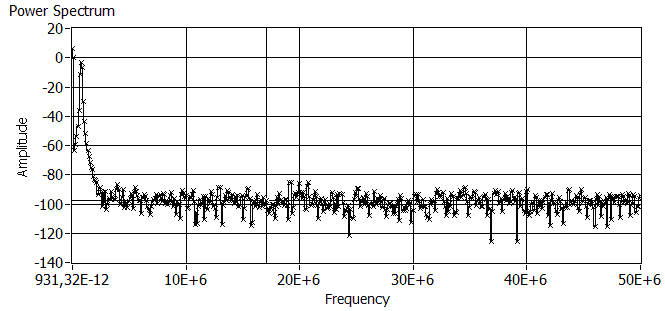

Board: LTC evaluation board. ENOB: 10,9 samples: 2048 file: F:\SU735_14Bit_ADC\SU735-1\Entwicklung\Messungen\Mit Signal Rigol 1MHz.adc signal: rigol

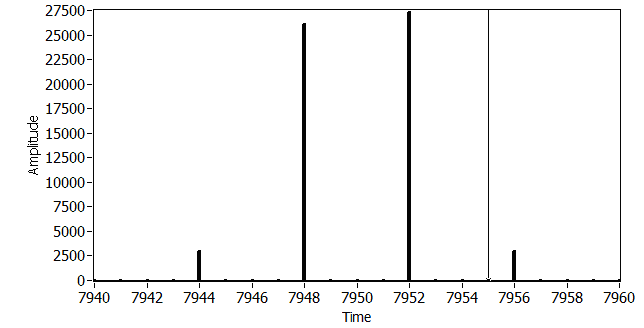

Board: DL709 7xADC mean: 7950 variance: 7,3 std. deviation: 2,7 input: no signal samples: ?? 12-Bits ADC

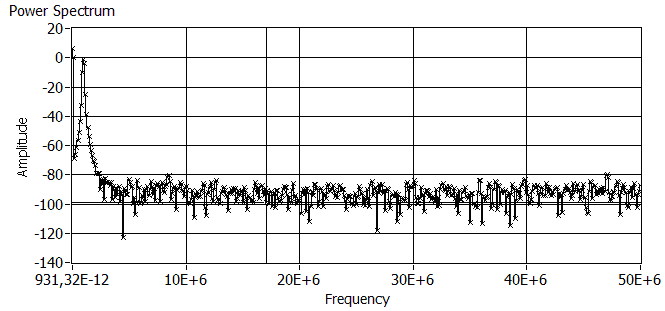

Board: DL709 7xADC ENOB: 10,32 samples: 2048 input: rigol 1,8 Vpp, f = 1MHz 12-Bits ADC

Board: DL709 7xADC mean: 7947,43 variance: 6,59 std. Deviation: 2,57 input: no signal samples: ?? 14-Bits ADC

Board: DL709 7xADC ENOB: 10,4 samples: 2048 input: rigol 1,8 Vpp, f = 1MHz 14-Bits ADC

Board: DL709 7xADC with USB isolator mean: 7948,33 variance: 6,73 std. Deviation: 2,59 input: no signal samples: ?? 14-Bits ADC