Difference between revisions of "SU750"

(→WB_DATA at 7) |

|||

| (One intermediate revision by the same user not shown) | |||

| Line 114: | Line 114: | ||

Bits 6..0 : | Bits 6..0 : | ||

| + | Address Range Data/Control Registers Function | ||

| + | 0x00-0x1F PLL0 Dynamic Access1 | ||

| + | 0x20-0x3F PLL1 Dynamic Access1 | ||

| + | 0x40-0x49 I2C Primary | ||

| + | 0x4A-0x53 I2C Secondary | ||

| + | 0x54-0x5D SPI | ||

| + | 0x5E-0x6F Timer/Counter | ||

| + | 0x70-0x75 Flash Memory (UFM/Configuration) | ||

| + | 0x76-0x77 EFB Interrupt Source | ||

| + | |||

| + | Bit 7 : write(1) or read(0). | ||

== WB_DATA at 7== | == WB_DATA at 7== | ||

| + | |||

| + | See WB_ADDR. | ||

| + | |||

| + | * Write cycle : | ||

| + | # write (address & 0x7F) | 0x80 to WB_ADDR | ||

| + | # write the data to WB_DATA. | ||

| + | |||

| + | * Read cycle : | ||

| + | # write address & 0x7F to WB_ADDR | ||

| + | # read the data from WB_DATA. | ||

= ADC configuration registers (the most essential) = | = ADC configuration registers (the most essential) = | ||

Latest revision as of 08:32, 12 January 2015

Contents

SU750 pin table (direction shown for the SU board!)

power in +5V 2 1 +5V in power LVTTL bidir SDA 4 3 SCL in LVTTL LVTTL out DATA<1> 6 5 DATA<0> out LVTTL LVTTL out DATA<3> 8 7 DATA<2> out LVTTL LVTTL out DATA<5> 10 9 DATA<4> out LVTTL LVTTL out DATA<7> 12 11 DATA<6> out LVTTL LVTTL out DATA<9> 14 13 DATA<8> out LVTTL LVTTL out DATA<11> 16 15 DATA<10> out LVTTL LVTTL out DATA<13> 18 17 DATA<12> out LVTTL LVTTL in TRIGG 20 19 VALID out LVTTL LVTTL in FREQ<2> 22 21 SPI_CONF in LVTTL LVTTL in FREQ<1> 24 23 FREQ<0> in LVTTL LVTTL in RESET 26 25 CLK_READ in LVTTL LVTTL out SDRD 28 27 SEn in LVTTL LVTTL in SCLKn 30 29 SDATA in LVTTL LVTTL out PGND<1> 32 31 PGND<0> out LVTTL LVTTL in CLKp 34 33 CLKn in LVTTL power in GND 36 35 GND in power

Differences to SU735:

ADC

SU735 SU750 LTC2261 ADS4149

Pinout

SU735 SU750 PIN GI_GATE (in) VALID (out) 19 SPARE<1> TRIGG (in) 20 SPARE<2> SPI_CONF (in) 21 SPARE<3> FREQ<2> (in) 22 (still not used in design) CLK_CPU CLK_READ 25 (was not used in the latest firmware of SU735) - GND 31, 32

Clocks

- CLKp, CLKn

SU750 should get ALWAYS 100 MHz at CLKp and CLKn! The SiLabs PLL creates depending on the two FREQ pins four frequencies for the ADC:

FREQ[1:0] Frequency, MHz 0 100 1 150 2 200 3 250

- CLK_READ can be 100 MHz or below, it is used to clock out the data from the internal memory

Output data:

VALID = 1 means valid output data (SU750), SU735 forwards directly the ADC data.

Trigger

TRIGG = 1 starts the data storing, shortly after triggering the readout is started as a complete block, with VALID=1 indicatiing valid data.

SPI configuration

SPI_CONF = 1 selects the internal configuration registers instead of the ADC (and disconnects the ADC SPI).

The SPI Word has 16 bits (like of the LT ADC), the upper 3 (MSB) bits are address, the next bit is read(0) or write(1), the other 12 (LSB) bits are data.

SPI configuration registers:

PRESAMPLES (10 bits) at 0

Number of presamples stored before the trigger

EVNT_SIZE (3 bits) at 1

evnt_size Event Size[samples] 000 16 001 32 010 64 011 128 100 256 101 512 110 1024 111 1024 (later 2048)

LED (7 bits) at 2

Bits 0..4 are for LEDs from top to bottom. Bit 5: when 0, display the "ok" of test pattern check for 0x2AAA -> 0x1555, else LED=Bit 3 Bit 6: when 0, display the "ok" of test pattern check for ramp, else LED=Bit 4

SEND_TP (2 bits) at 3

Bit 1 : when 0 => normal ADC data else testpattern data Bit 0 : when 0 => 0x3FFF -> 0x0000 else 0x2AAA -> 0x1555

This test pattern is send at 100 MHz (CLK_READ) continuously by the FPGA and can be checked in the LogicBox.

FREQ_CNT at 4

Read the ADC clocks for 1000 logic box (CLK_READ) clocks => divide by 10 to get the freq in MHz (provided CLK_READ is 100 MHz).

TP_CHECK at 5

Bit 1 : ok for ramp pattern from ADC Bit 0 : ok for 0x2AAA -> 0x1555 pattern from ADC

This test pattern is send by the ADC and checked continuously in the FPGA for errors. The flags are cleared by any error and can be set by writing anything to this address. So the typical test procedure is 1) set the frequency and test pattern in ADC; 2) wait a bit and clear the errors by writing to TP_CHECK; 3) wait some seconds (or more) and read the two flags.

WB_ADDR at 6

Access to the Wishbone bus on the Lattice FPGA.

Bits 6..0 : Address Range Data/Control Registers Function 0x00-0x1F PLL0 Dynamic Access1 0x20-0x3F PLL1 Dynamic Access1 0x40-0x49 I2C Primary 0x4A-0x53 I2C Secondary 0x54-0x5D SPI 0x5E-0x6F Timer/Counter 0x70-0x75 Flash Memory (UFM/Configuration) 0x76-0x77 EFB Interrupt Source

Bit 7 : write(1) or read(0).

WB_DATA at 7

See WB_ADDR.

- Write cycle :

- write (address & 0x7F) | 0x80 to WB_ADDR

- write the data to WB_DATA.

- Read cycle :

- write address & 0x7F to WB_ADDR

- read the data from WB_DATA.

ADC configuration registers (the most essential)

(for the full description see the datasheet)

The default values of all registers are 0x00, please write to the unspecified bits 0!

RESET, SDO at 0x00

Bit 1 is RESET (reset the ADC when 1), bit 0 is READOUT (set the SPI interface in read mode)

HIGH PERF MODE 1 at 0x03

Bits 1:0 should be set to 1 for best performance

GAIN, TEST PATTERN at 0x25

Bits 7:3 control the digital gain, best don't use it (Bit 3 at 1, the rest at 0) Bits 2:0 Output 000 Normal operation (ADC data) 001 All 0s 010 All 1s 011 Toggle pattern, 0x2AAA -> 0x1555 100 Digital ramp (14-bit counter) 101 Custom pattern (use registers 0x3F and 0x40) 110, 111 Unused

Note: in order to send test pattern please disable the low latency mode in register 0x42 !!!

LVDS/CMOS, CLK OUT at 0x41

Bits 7:6 : select the output level, either LVDS DDR (01) or CMOS SDR (11), when X0 the DFS pin controls the selection. Bits 5:3 : CMOS CLKOUT strength, 00, 01, 10, 11 for max..min Bit 3 : enable CLKOUT RISE Bits 2:1 : CLKOUT RISE position, for CMOS 00 Default (as in datasheet) 01 Setup reduces by 100 ps, hold increases by 100 ps 10 Setup reduces by 200 ps, hold increases by 200 ps 11 Setup reduces by 1.5 ns, hold increases by 1.5 ns Bit 0 : ENABLE CLKOUT FALL

CLKOUT FALL, LOW LATENCY, STBY at 0x42

Bits 7:6 : CLKOUT FALL position, for CMOS 00 Default (as in datasheet) 01 Falling edge advanced by 100 ps 10 Falling edge advanced by 200 ps 11 Falling edge advanced by 1.5 ns Bit 3 : DIS LOW LATENCY, 0 - low latency is enabled, 1 - low latency is disabled Bit 2 : STBY - standby mode, 0 for normal operation, 1 for standby with fast wake-up time

Note: Digital functions such as gain, test pattern and offset correction are disabled in low latency mode!!!

HIGH PERF MODE 2 at 0x4A

Bit 0 : 0 - default performance, 1 - best performance

Measurements

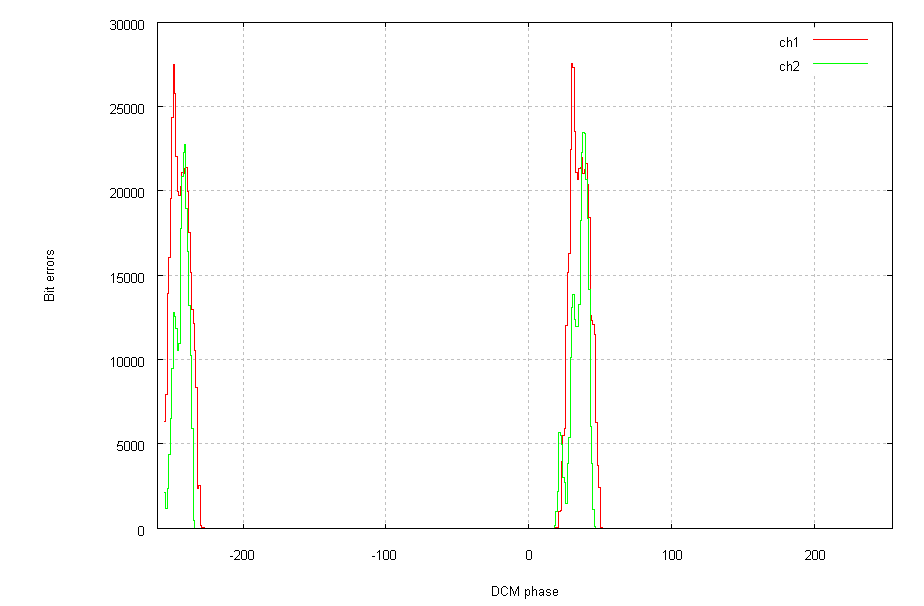

Bit errors for the data transfer from the SU750-FPGA to the LogicBox FPGA

Two SU750 at slots 1 and 2 are configured to send test pattern data, once 00-FF, once AA-55

Base board : DL709-1 with XC3S5000 device. SU750 boards : with LCMXO2-2000HC-6 device.

Bit errors for the data transfer from the ADC to the SU750-FPGA

With both AA-55 and ramp test patterns depending on reg 0x41 in ADC Bits 2:1 : CLKOUT RISE position, for CMOS 00 no errors 01 no errors 10 no errors 11 errors

Recommended: at 00.