Difference between revisions of "SU748"

(→Front panel) |

(→Power consumption) |

||

| (5 intermediate revisions by the same user not shown) | |||

| Line 14: | Line 14: | ||

= Back Connector = | = Back Connector = | ||

| − | + | SU748 pin table first connector (direction shown for the SU board!) | |

| − | + | power in +5V 2 1 +5V in power | |

| + | * out I2C_SCL_FX3 4 3 I2C_SDA_FX3 bidir * | ||

| + | power in GND 6 5 GND in power | ||

| + | power in GND 8 7 DQ0 bidir LVTTL | ||

| + | LVTTL bidir DQ1 10 9 DQ5 bidir LVTTL | ||

| + | LVTTL bidir DQ2 12 11 GND in power | ||

| + | power in GND 14 13 DQ3 bidir LVTTL | ||

| + | LVTTL bidir DQ4 16 15 DQ6 bidir LVTTL | ||

| + | LVTTL bidir DQ7 18 17 GND in power | ||

| + | power in GND 20 19 DQ15 bidir LVTTL | ||

| + | LVTTL bidir DQ8 22 21 DQ9 bidir LVTTL | ||

| + | LVTTL bidir DQ14 24 23 GND in power | ||

| + | power in GND 26 25 DQ10 bidir LVTTL | ||

| + | LVTTL bidir DQ12 28 27 DQ13 bidir LVTTL | ||

| + | LVTTL bidir DQ11 30 29 GND in power | ||

| + | * bidir UART_RX/SPI_MOSI 32 31 UART_TX/SPI_MISO bidir * | ||

| + | * bidir UART_CTS/SPI_SSN 34 33 GPIO[16]_CLK in LVTTL | ||

| + | power in GND 36 35 GND in power | ||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | + | SU748 pin table second connector (direction shown for the SU board!) | |

| − | + | power in +5V 2 1 +5V in power | |

| + | LVTTL in GPIO[19]_\SLOE 4 3 GPIO[17]_\SLCS in LVTTL | ||

| + | LVTTL in GPIO[24]_\PKTEND 6 5 GPIO[18]_\SLWR in LVTTL | ||

| + | LVTTL in GPIO[20]_\SLRD 8 7 GPIO[21]_FLAGA out LVTTL | ||

| + | LVTTL out GPIO[22]_FLAGB 10 9 GPIO[28]_A1 in LVTTL | ||

| + | LVTTL in GPIO[29]_A0 12 11 GND in power | ||

| + | power in GND 14 13 DQ17 bidir LVTTL | ||

| + | LVTTL bidir DQ20 16 15 DQ23 bidir LVTTL | ||

| + | LVTTL bidir DQ16 18 17 GND in power | ||

| + | power in GND 20 19 DQ18 bidir LVTTL | ||

| + | LVTTL bidir DQ19 22 21 DQ21 bidir LVTTL | ||

| + | LVTTL bidir DQ22 24 23 GND in power | ||

| + | power in GND 26 25 DQ26 bidir LVTTL | ||

| + | LVTTL bidir DQ25 28 27 DQ28 bidir LVTTL | ||

| + | LVTTL bidir DQ24 30 29 GND in power | ||

| + | LVTTL bidir DQ27 32 31 DQ30 bidir LVTTL | ||

| + | LVTTL bidir DQ31 34 33 DQ29 bidir LVTTL | ||

| + | power in GND 36 35 GND in power | ||

| − | + | = Power consumption = | |

| − | + | +5V -> ?? mA | |

= Measurement = | = Measurement = | ||

Latest revision as of 12:02, 7 August 2015

Contents

Description

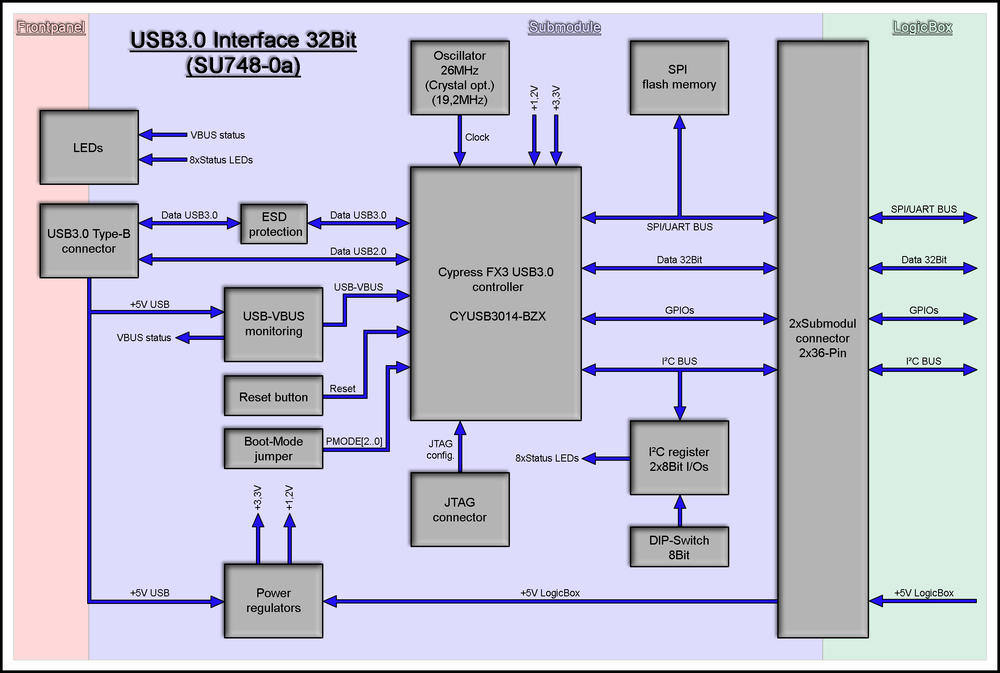

This module provides a super speed USB3.0 Interface for the LogicBox in association with the Cypress FX3 USB3.0 controller. Due to the 32-Bit parallel Data-BUS, the submdoule was designed as a double SU-Board with two SU-Connectors. The hole board can be supplied by the +5V-supply of the USB-Port or the +5V-supply of the LogicBox. To protect the FX3 controller against a faulty VBUS voltage from the USB-Port, the USB charger port protection chip TPD4S014 was used. The FX3-Chip provides several serial interfaces like I²S, I²C, SPI and UART to connect to external peripherals. With the implemented I²C register PCA9555 configured by I²C or the 8-Pin DIP-Switch, some status information can be displayed on eight LEDs at the frontpanel.

Block Diagram

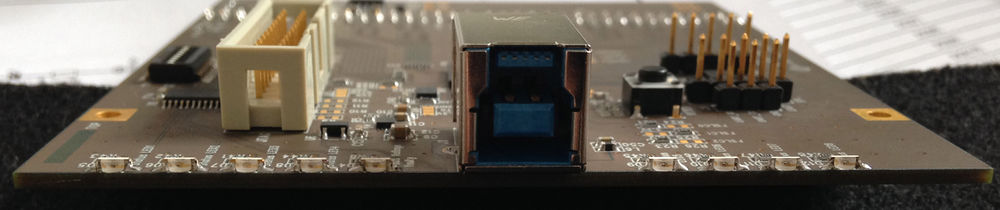

Front panel

Back Connector

SU748 pin table first connector (direction shown for the SU board!)

power in +5V 2 1 +5V in power

* out I2C_SCL_FX3 4 3 I2C_SDA_FX3 bidir *

power in GND 6 5 GND in power

power in GND 8 7 DQ0 bidir LVTTL

LVTTL bidir DQ1 10 9 DQ5 bidir LVTTL

LVTTL bidir DQ2 12 11 GND in power

power in GND 14 13 DQ3 bidir LVTTL

LVTTL bidir DQ4 16 15 DQ6 bidir LVTTL

LVTTL bidir DQ7 18 17 GND in power

power in GND 20 19 DQ15 bidir LVTTL

LVTTL bidir DQ8 22 21 DQ9 bidir LVTTL

LVTTL bidir DQ14 24 23 GND in power

power in GND 26 25 DQ10 bidir LVTTL

LVTTL bidir DQ12 28 27 DQ13 bidir LVTTL

LVTTL bidir DQ11 30 29 GND in power

* bidir UART_RX/SPI_MOSI 32 31 UART_TX/SPI_MISO bidir *

* bidir UART_CTS/SPI_SSN 34 33 GPIO[16]_CLK in LVTTL

power in GND 36 35 GND in power

SU748 pin table second connector (direction shown for the SU board!)

power in +5V 2 1 +5V in power LVTTL in GPIO[19]_\SLOE 4 3 GPIO[17]_\SLCS in LVTTL LVTTL in GPIO[24]_\PKTEND 6 5 GPIO[18]_\SLWR in LVTTL LVTTL in GPIO[20]_\SLRD 8 7 GPIO[21]_FLAGA out LVTTL LVTTL out GPIO[22]_FLAGB 10 9 GPIO[28]_A1 in LVTTL LVTTL in GPIO[29]_A0 12 11 GND in power power in GND 14 13 DQ17 bidir LVTTL LVTTL bidir DQ20 16 15 DQ23 bidir LVTTL LVTTL bidir DQ16 18 17 GND in power power in GND 20 19 DQ18 bidir LVTTL LVTTL bidir DQ19 22 21 DQ21 bidir LVTTL LVTTL bidir DQ22 24 23 GND in power power in GND 26 25 DQ26 bidir LVTTL LVTTL bidir DQ25 28 27 DQ28 bidir LVTTL LVTTL bidir DQ24 30 29 GND in power LVTTL bidir DQ27 32 31 DQ30 bidir LVTTL LVTTL bidir DQ31 34 33 DQ29 bidir LVTTL power in GND 36 35 GND in power

Power consumption

+5V -> ?? mA

Measurement

Version 0

Compatibility

This module is compatible with all base boards