Difference between revisions of "Clock generator (CLOCK)"

(Created page with "= LogicPool (CLOCK) = A clock can be implemented using the GATEGEN VHDL modul, due to this the address and register map is the same as by the GATEGEN == LabVIEW Vi == === ...") |

(→LabVIEW Vi) |

||

| (One intermediate revision by the same user not shown) | |||

| Line 1: | Line 1: | ||

= LogicPool (CLOCK) = | = LogicPool (CLOCK) = | ||

| − | A clock can be implemented using the GATEGEN VHDL | + | A clock can be implemented using the GATEGEN VHDL module, due to this the address and register map is the same as by the GATEGEN |

== LabVIEW Vi == | == LabVIEW Vi == | ||

| Line 7: | Line 7: | ||

=== CLOCK.vi === | === CLOCK.vi === | ||

| − | + | CLOCK module for generating free running clocks. | |

| + | All frequencies on output CLK are derived from the system clock (100 MHz) by a divider. | ||

[[File:CLOCKc.png]] | [[File:CLOCKc.png]] | ||

| − | |||

The meaning of almost inputs and outputs of this Vi depends on the input "Function". The global inputs and outputs does not depend on the "function" input: | The meaning of almost inputs and outputs of this Vi depends on the input "Function". The global inputs and outputs does not depend on the "function" input: | ||

| Line 18: | Line 18: | ||

=== Glogal Inputs === | === Glogal Inputs === | ||

| − | + | GATEGEN#: number of gate generator to be configured as clock (1..255). | |

USB In: Handle to the LogicBox (create by open.vi), if not connected will take a global. parameter, this only works with one LogicBox at a time. | USB In: Handle to the LogicBox (create by open.vi), if not connected will take a global. parameter, this only works with one LogicBox at a time. | ||

| Line 33: | Line 33: | ||

| − | Connect: enable, configurate and set | + | Connect: enable, configurate and set the trigger driver signal. |

| − | + | Inputs: | |

| − | + | "Freq" set the clock frequency | |

| − | + | "Enable" enable/disbale Clock (synchronous) | |

| − | " | + | "Width" specifies lenght of High state in 10 ns (=0 generates 50% duty cycle!) |

| − | + | ||

| + | Outputs: | ||

| + | "CLK" signal number in which the clock is generated | ||

| − | Get | + | Get CLK: |

| − | + | Outputs: "CLK" return output state of CLK | |

| − | |||

| − | |||

| − | Set | + | Set ENABLE: |

| − | + | Input: "ENABLE" enable/disbale Clock (synchronous) | |

| − | + | ||

| − | + | Gen/Hz: | |

| + | Output: "Gen" current generated frequency in Hz | ||

=== Example VIs === | === Example VIs === | ||

| − | + | LP_CLOCK_test.vi | |

Latest revision as of 10:31, 10 May 2016

Contents

LogicPool (CLOCK)

A clock can be implemented using the GATEGEN VHDL module, due to this the address and register map is the same as by the GATEGEN

LabVIEW Vi

CLOCK.vi

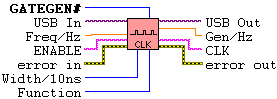

CLOCK module for generating free running clocks. All frequencies on output CLK are derived from the system clock (100 MHz) by a divider.

The meaning of almost inputs and outputs of this Vi depends on the input "Function". The global inputs and outputs does not depend on the "function" input:

Glogal Inputs

GATEGEN#: number of gate generator to be configured as clock (1..255).

USB In: Handle to the LogicBox (create by open.vi), if not connected will take a global. parameter, this only works with one LogicBox at a time.

error in: error handling input

Global Outputs

USB out: Handle to the LogicBox.

error out: error handling output

Functions

Connect: enable, configurate and set the trigger driver signal.

Inputs:

"Freq" set the clock frequency

"Enable" enable/disbale Clock (synchronous)

"Width" specifies lenght of High state in 10 ns (=0 generates 50% duty cycle!)

Outputs:

"CLK" signal number in which the clock is generated

Get CLK: Outputs: "CLK" return output state of CLK

Set ENABLE: Input: "ENABLE" enable/disbale Clock (synchronous)

Gen/Hz: Output: "Gen" current generated frequency in Hz

Example VIs

LP_CLOCK_test.vi