Difference between revisions of "SU704"

(→Version 0) |

(→Description) |

||

| (11 intermediate revisions by the same user not shown) | |||

| Line 3: | Line 3: | ||

= Description = | = Description = | ||

| + | |||

| + | This module consist of 5 channel digital input/output (DIO) and 5 LEDs. Each channel can be set to work under the NIM or TTL standard independently, both of them can drive 50 Ohm impedances. If you use a channel as NIM input a 50 Ohm termination resistor must be connected to avoid reflections, this resistor can be connected through software in the version 1 of the hardware or with the help of a jumper in version 2. For all signals was used LEMO connectors. The maximal work frequency is 100 MHz. | ||

| + | |||

| + | There are three hardware version of this module. The Version 0 is not used any more. The only difference between the version 1 and 2 is that in version 1 the termination resistor can be connected through software and by the version 2 a solder jumper must to be set. The version 2 should have a better noise performance. | ||

| + | |||

| + | The DIO/LED number has been inverted in the FPGA software to match the order of the SU700 module. The LED1 in FPGA connector corresponds the LED5 at the front panel. | ||

| + | |||

| Line 11: | Line 18: | ||

! scope="col" | Input impedance (50 Ohm/open) | ! scope="col" | Input impedance (50 Ohm/open) | ||

! scope="col" | Standard (TTL/NIM) | ! scope="col" | Standard (TTL/NIM) | ||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

|- | |- | ||

|1 | |1 | ||

| Line 27: | Line 29: | ||

|solder jumper | |solder jumper | ||

|} | |} | ||

| + | |||

| + | |||

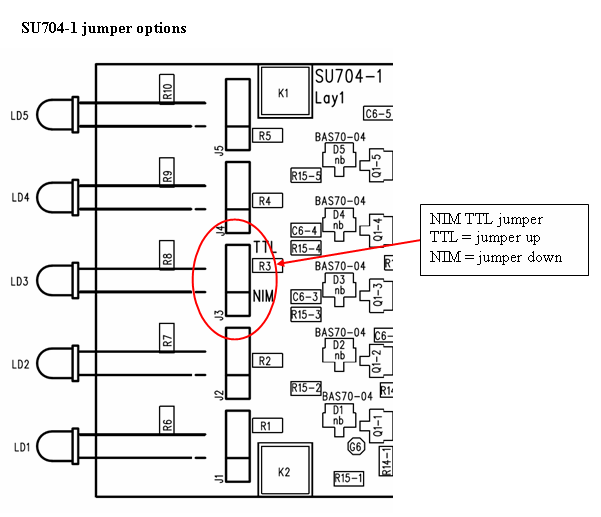

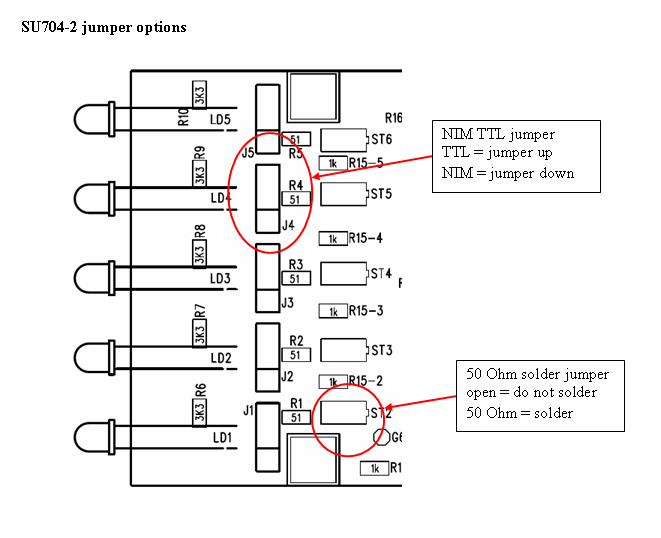

| + | [[File:SU704-1_jumper_option.png]] [[File:SU704-2_jumper_option.png]] | ||

= Block Diagram = | = Block Diagram = | ||

| + | |||

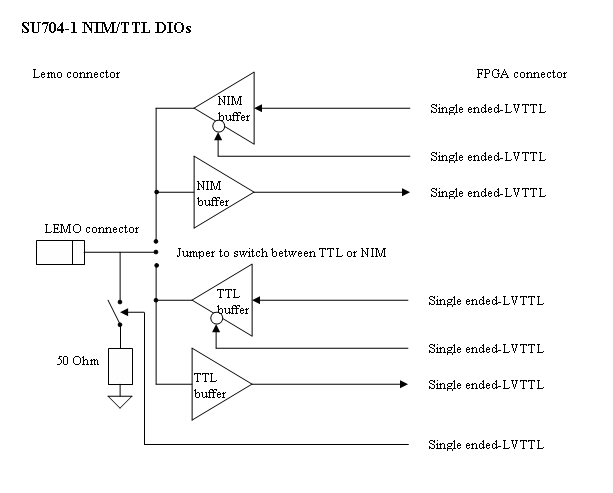

| + | [[File:SU704-1_block_diagram.png]] | ||

| + | |||

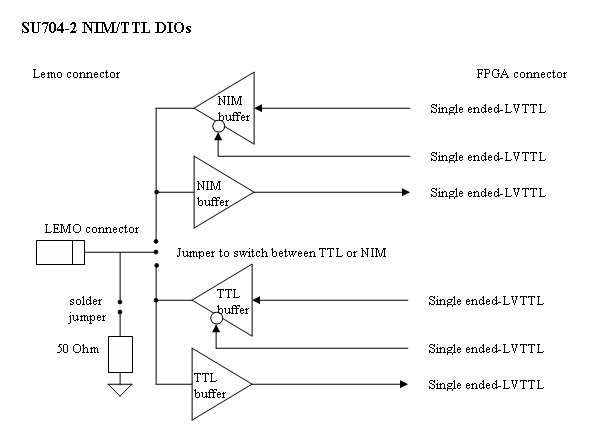

| + | [[File:SU704-2_block_diagram.png]] | ||

= Front planel = | = Front planel = | ||

| − | + | == Version 1 and 2 == | |

| − | + | ||

| − | + | [[File:SU704_Front_panel.png]] | |

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

= Back Connector = | = Back Connector = | ||

| Line 128: | Line 61: | ||

LVTTL in LED<3> 18 17 LED<2> out LVTTL | LVTTL in LED<3> 18 17 LED<2> out LVTTL | ||

LVTTL in LED<1> 20 19 - - NC | LVTTL in LED<1> 20 19 - - NC | ||

| − | NC | + | NC - - 22 21 - - NC |

| − | NC | + | NC - - 24 23 - - NC |

| − | NC | + | NC - - 26 25 - - NC |

| − | NC | + | NC - - 28 27 - - NC |

| − | NC | + | NC - - 30 29 - - NC |

| − | NC | + | NC - - 32 31 - - NC |

NC - - 34 33 - - NC | NC - - 34 33 - - NC | ||

power in - 36 35 GND in power | power in - 36 35 GND in power | ||

Latest revision as of 09:16, 10 September 2014

Contents

Description

This module consist of 5 channel digital input/output (DIO) and 5 LEDs. Each channel can be set to work under the NIM or TTL standard independently, both of them can drive 50 Ohm impedances. If you use a channel as NIM input a 50 Ohm termination resistor must be connected to avoid reflections, this resistor can be connected through software in the version 1 of the hardware or with the help of a jumper in version 2. For all signals was used LEMO connectors. The maximal work frequency is 100 MHz.

There are three hardware version of this module. The Version 0 is not used any more. The only difference between the version 1 and 2 is that in version 1 the termination resistor can be connected through software and by the version 2 a solder jumper must to be set. The version 2 should have a better noise performance.

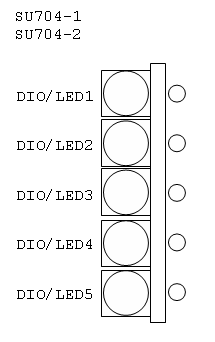

The DIO/LED number has been inverted in the FPGA software to match the order of the SU700 module. The LED1 in FPGA connector corresponds the LED5 at the front panel.

| Version | -5V converter | Input impedance (50 Ohm/open) | Standard (TTL/NIM) |

|---|---|---|---|

| 1 | DC-DC | software | jumper |

| 2 | Linear | solder jumper | solder jumper |

Block Diagram

Front planel

Version 1 and 2

Back Connector

Version 0

SU704 pin table (direction shown for the SU board!)

power in +5V 2 1 +5V in power LVTTL in IN<4> 4 3 OUT<4> out LVTTL LVTTL in IN<3> 6 5 OUT<3> out LVTTL LVTTL in IN<2> 8 7 OUT<2> out LVTTL LVTTL in IN<1> 10 9 OUT<1> out LVTTL LVTTL in NIM<4> 12 11 NIM<3> out LVTTL LVTTL in NIM<2> 14 13 NIM<1> in LVTTL LVTTL in LED<5> 16 15 LED<4> out LVTTL LVTTL in LED<3> 18 17 LED<2> out LVTTL LVTTL in LED<1> 20 19 - - NC NC - - 22 21 - - NC NC - - 24 23 - - NC NC - - 26 25 - - NC NC - - 28 27 - - NC NC - - 30 29 - - NC NC - - 32 31 - - NC NC - - 34 33 - - NC power in - 36 35 GND in power

Version 1

SU704 pin table (direction shown for the SU board!)

power in +5V 2 1 +5V in power

LVTTL in OUTP<5> 4 3 INTTL<5> out LVTTL

LVTTL in OE_n<5> 6 5 INECL<5> out LVTTL

LVTTL in TERM<5> 8 7 LED_n<5> in LVTTL

LVTTL in OUTP<4> 10 9 INTTL<4> out LVTTL

LVTTL in OE_n<4> 12 11 INECL<4> out LVTTL

LVTTL in TERM<4> 14 13 LED_n<4> in LVTTL

LVTTL in OUTP<3> 16 15 INTTL<3> out LVTTL

LVTTL in OE_n<3> 18 17 INECL<3> out LVTTL

LVTTL in TERM<3> 20 19 LED_n<3> in LVTTL

LVTTL in OUTP<2> 22 21 INTTL<2> out LVTTL

LVTTL in OE_n<2> 24 23 INECL<2> out LVTTL

LVTTL in TERM<2> 26 25 LED_n<2> in LVTTL

LVTTL in OUTP<1> 28 27 INTTL<1> out LVTTL

LVTTL in OE_n<1> 30 29 INECL<1> out LVTTL

LVTTL in TERM<1> 32 31 LED_n<1> in LVTTL

NC - - 34 33 - - NC

power in GND 36 35 GND in power

Version 2

SU704 pin table (direction shown for the SU board!)

power in +5V 2 1 +5V in power

LVTTL in OUTP<5> 4 3 INTTL<5> out LVTTL

LVTTL in OE_n<5> 6 5 INECL<5> out LVTTL

NC in - 8 7 LED_n<5> in LVTTL

LVTTL in OUTP<4> 10 9 INTTL<4> out LVTTL

LVTTL in OE_n<4> 12 11 INECL<4> out LVTTL

NC in - 14 13 LED_n<4> in LVTTL

LVTTL in OUTP<3> 16 15 INTTL<3> out LVTTL

LVTTL in OE_n<3> 18 17 INECL<3> out LVTTL

NC in - 20 19 LED_n<3> in LVTTL

LVTTL in OUTP<2> 22 21 INTTL<2> out LVTTL

LVTTL in OE_n<2> 24 23 INECL<2> out LVTTL

NC in - 26 25 LED_n<2> in LVTTL

LVTTL in OUTP<1> 28 27 INTTL<1> out LVTTL

LVTTL in OE_n<1> 30 29 INECL<1> out LVTTL

LVTTL in - 32 31 LED_n<1> in LVTTL

NC - - 34 33 - - NC

power in GND 36 35 GND in power