Difference between revisions of "SU735"

m |

m |

||

| Line 50: | Line 50: | ||

| − | '''Ab SVN Version 25''' CLK_CPU | + | '''Ab SVN Version 25''' CLK_CPU wird nicht mehr benötigt, es wird ein interner Oscillator benutzt. Jede Änderung der 2 Bits Freq<1:0> oder ein RESET Pulse startet die Initialisierung des Clock-Cleaner ICs. |

Revision as of 15:09, 24 January 2014

SU735 pin table (direction shown for the SU board!)

prototype

power in +5V 2 1 +5V in power

LVTTL in CLKp 4 3 CLKn in LVTTL

NC - - 6 5 - - NC

LVTTL out DATA<1> 8 7 DATA<0> out LVTTL

LVTTL out DATA<3> 10 9 DATA<2> out LVTTL

LVTTL out DATA<5> 12 11 DATA<4> out LVTTL

LVTTL out DATA<7> 14 13 DATA<6> out LVTTL

LVTTL out DATA<9> 16 15 DATA<8> out LVTTL

LVTTL out DATA<11> 18 17 DATA<10> out LVTTL

LVTTL out DATA<13> 20 19 DATA<12> out LVTTL

LVTTL in SPARE<1> 22 21 SPARE<0> in LVTTL

LVTTL in SPARE<3> 24 23 SPARE<2> in LVTTL

LVTTL in SPARE<5> 26 25 SPARE<4> in LVTTL

LVTTL in RESET 28 27 SPARE<6> in LVTTL

LVTTL in SCL 30 29 SDA bidir LVTTL

LVTTL out SDRD 32 31 SEn in LVTTL

LVTTL in SDATA 34 33 SCLKn in LVTTL

power in GND 36 35 GND in power

production version

power in +5V 2 1 +5V in power

LVTTL bidir SDA 4 3 SCL in LVTTL

LVTTL out DATA<1> 6 5 DATA<0> out LVTTL

LVTTL out DATA<3> 8 7 DATA<2> out LVTTL

LVTTL out DATA<5> 10 9 DATA<4> out LVTTL

LVTTL out DATA<7> 12 11 DATA<6> out LVTTL

LVTTL out DATA<9> 14 13 DATA<8> out LVTTL

LVTTL out DATA<11> 16 15 DATA<10> out LVTTL

LVTTL out DATA<13> 18 17 DATA<12> out LVTTL

LVTTL in SPARE<1> 20 19 GI_GATE in LVTTL

LVTTL in SPARE<3> 22 21 SPARE<2> in LVTTL

LVTTL in FREQ<1> 24 23 FREQ<0> in LVTTL

LVTTL in RESET 26 25 CLK_CPU in LVTTL

LVTTL out SDRD 28 27 SEn in LVTTL

LVTTL in SCLKn 30 29 SDATA in LVTTL

NC - - 32 31 - - NC

LVTTL in CLKp 34 33 CLKn in LVTTL

power in GND 36 35 GND in power

Ab SVN Version 25 CLK_CPU wird nicht mehr benötigt, es wird ein interner Oscillator benutzt. Jede Änderung der 2 Bits Freq<1:0> oder ein RESET Pulse startet die Initialisierung des Clock-Cleaner ICs.

Modifikation für R. Schicker: 2 digitalle Ausgänge auf den LEMOs J2 und J3 (U5 und viele Widerstände müsen weg).

Spare<1> und Spare<2> werden zu den 2 LEMOs durch das Lattice FPGA weitergeleitet.

Measurement

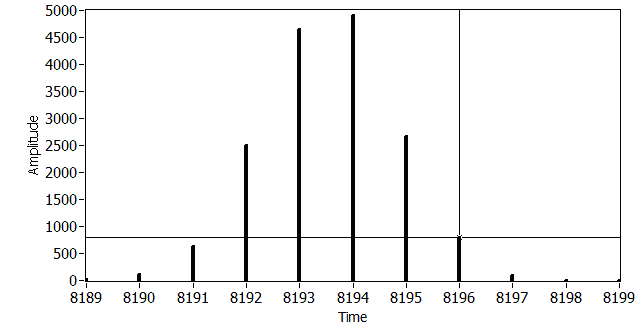

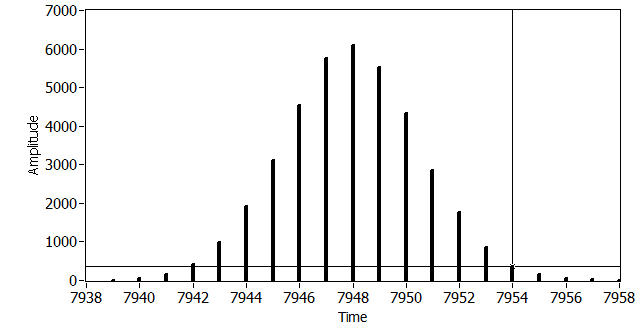

Board: LTC evaluation board. mean: 8193,55 variance: 1,58 std. deviation: 1,26 input: no signal samples: 16384 file: F:\SU735_14Bit_ADC\SU735-1\Entwicklung\Messungen\Ohne Signal.adc

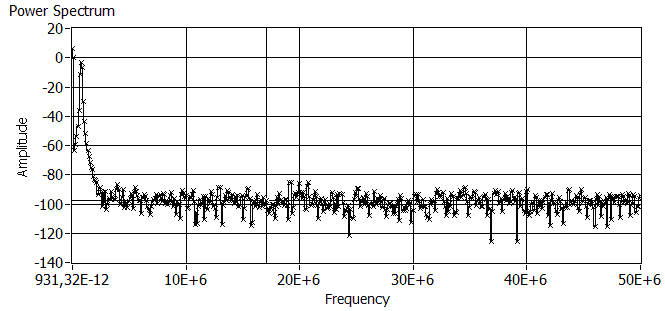

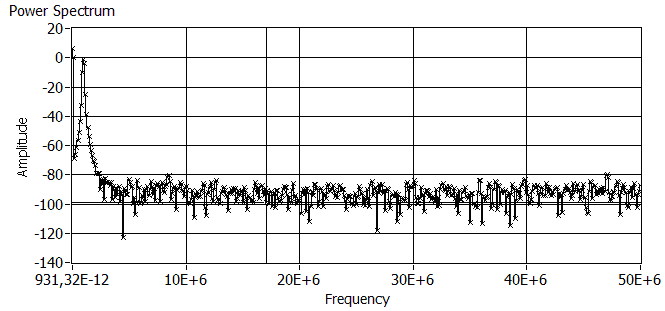

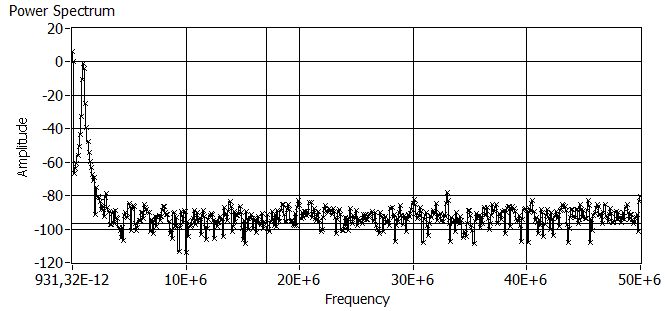

Board: LTC evaluation board. ENOB: 10,9 samples: 2048 file: F:\SU735_14Bit_ADC\SU735-1\Entwicklung\Messungen\Mit Signal Rigol 1MHz.adc signal: rigol

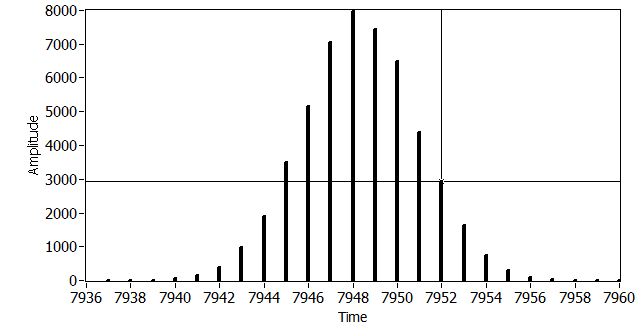

Board: DL709 7xADC mean: 7950 variance: 7,3 std. deviation: 2,7 input: no signal samples: ?? 12-Bits ADC

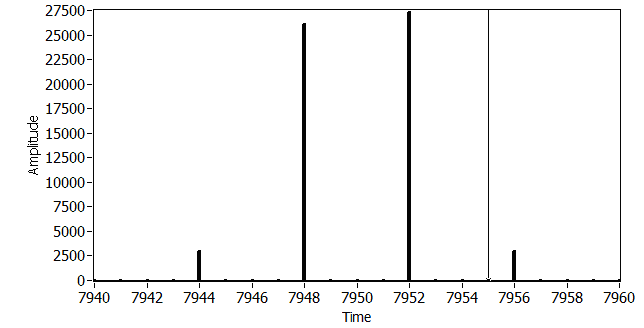

Board: DL709 7xADC ENOB: 10,32 samples: 2048 input: rigol 1,8 Vpp, f = 1MHz 12-Bits ADC

Board: DL709 7xADC mean: 7947,43 variance: 6,59 std. Deviation: 2,57 input: no signal samples: ?? 14-Bits ADC

Board: DL709 7xADC ENOB: 10,4 samples: 2048 input: rigol 1,8 Vpp, f = 1MHz 14-Bits ADC

Board: DL709 7xADC with USB isolator mean: 7948,33 variance: 6,73 std. Deviation: 2,59 input: no signal samples: ?? 14-Bits ADC