Difference between revisions of "SU717"

(→Version 0) |

(→Version 0) |

||

| Line 25: | Line 25: | ||

{| border="1" class="wikitable" | {| border="1" class="wikitable" | ||

| − | |+ | + | |+ Front panel connectors and controls |

! scope="col" | Name | ! scope="col" | Name | ||

! scope="col" | Type | ! scope="col" | Type | ||

| Line 53: | Line 53: | ||

|Potentiometer | |Potentiometer | ||

|1x | |1x | ||

| − | | | + | | |

|Cancel the integrator bias current | |Cancel the integrator bias current | ||

|} | |} | ||

Latest revision as of 08:46, 25 February 2014

Contents

Description

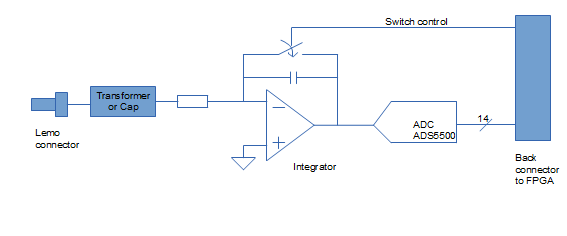

This module is a charge to digital converter. It consists of 3 blocks:

1) Front end (Signal conditioning) 2) FPGA controlled integrator 3) Analog to digital converter

The front end consist of a LEMO connector and after that can be found a RF transformer or a capacitor, or can be connected direct to the integrator input. The detector signal should be ac coupled to avoid dc errors.

The integrator is based on an operation amplifier and a TTL controlled switch to reset the capacitor charge. In this way the integration time can be set through an external control signal.

The last stage is a 14-Bit analog to digital converter and it can be run up to 100MHz from Texas instruments ADS5500. All ADC control and data signals are routed to the sub-module back connector.

Block Diagram

Version 0

Front planel

Version 0

| Name | Type | Qty. | Dir. | Function |

|---|---|---|---|---|

| Analog input | LEMO connector | 1x | input | Detector input |

| DIO | LEMO connector | 1x | input/output | Digital input/output (LVTTL) |

| LED | Led | 1x | Led to show some information | |

| POT | Potentiometer | 1x | Cancel the integrator bias current |

Back Connector

Version 0

SU717 pin table (direction shown for the SU board!)

power in +5V 2 1 +5V in power

LVTTL in RESET 4 3 CLKout out LVTTL

LVTTL out DATA<0> 6 5 DATA<1> out LVTTL

LVTTL out DATA<2> 8 7 DATA<3> out LVTTL

LVTTL out DATA<4> 10 9 DATA<5> out LVTTL

LVTTL out DATA<6> 12 11 DATA<7> out LVTTL

LVTTL out DATA<8> 14 13 DATA<9> out LVTTL

LVTTL out DATA<10> 16 15 DATA<11> out LVTTL

LVTTL out DATA<12> 18 17 DATA<13> out LVTTL

NC - - 20 19 SCLKn in LVTTL

LVTTL in SDATA 22 21 SEn in LVTTL

LVTTL in CLKp 24 23 CLKn in LVTTL

LVTTL in DIO_OUT 26 25 DIO_OEn in LVTTL

LVTTL in QRESETn 28 27 DIO_IN out LVTTL

LVTTL in QSHORTn 30 29 - - NC

NC - - 32 31 LEDn in LVTTL

NC - - 34 33 - - NC

power in GND 36 35 GND in power