Difference between revisions of "SU753"

m |

m |

||

| Line 32: | Line 32: | ||

[[File:su753-3.png]] | [[File:su753-3.png]] | ||

| + | |||

| + | Rising edge, MAX14900E, one channel without load and one channel loaded with 10k || 100pF: | ||

[[File:su753-4.png]] | [[File:su753-4.png]] | ||

| + | |||

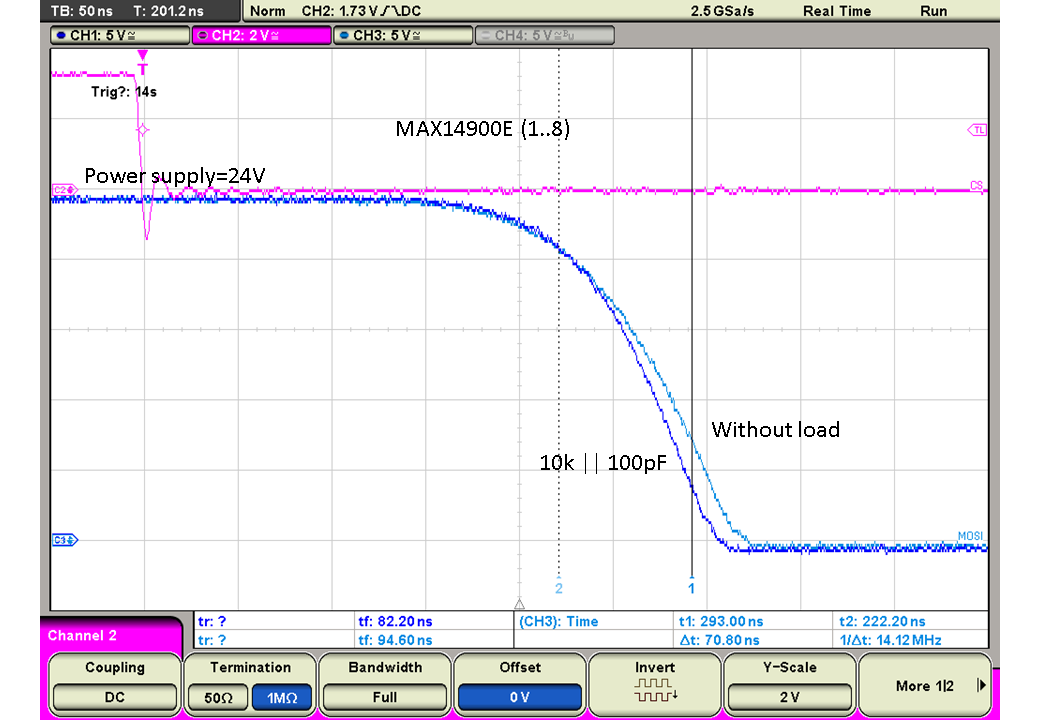

| + | Falling edge, MAX14900E, one channel without load and one channel loaded with 10k || 100pF: | ||

[[File:su753-5.png]] | [[File:su753-5.png]] | ||

| + | |||

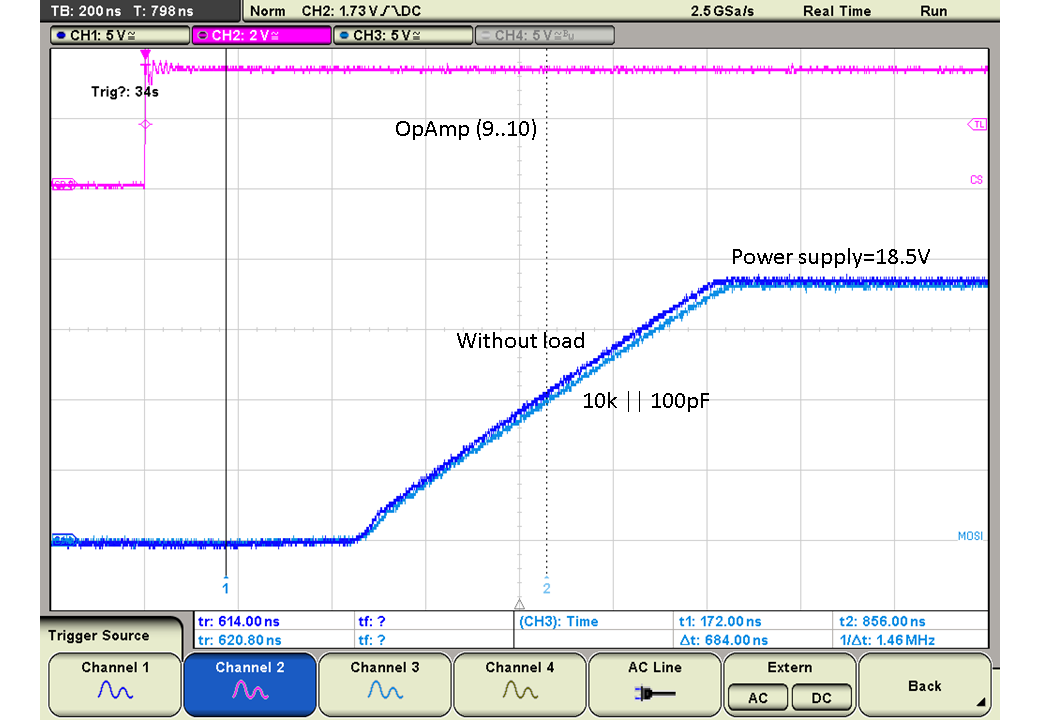

| + | Rising edge, Op Ampl, one channel without load and one channel loaded with 10k || 100pF: | ||

[[File:su753-6.png]] | [[File:su753-6.png]] | ||

| + | |||

| + | Falling edge, Op Ampl, one channel without load and one channel loaded with 10k || 100pF: | ||

[[File:su753-7.png]] | [[File:su753-7.png]] | ||

Revision as of 14:31, 13 April 2016

SU753 pin table (direction shown for the SU board!)

power in +5V 2 1 +5V in power

NC - - 4 3 - - NC

NC - - 6 5 - - NC

NC - - 8 7 - - NC

NC - - 10 9 - - NC

NC - - 12 11 - - NC

LVTTL in DATA<10> 14 13 - - NC

LVTTL in DATA<9> 16 15 - - NC

LVTTL in EN 18 17 - - NC

LVTTL in SRIAL 20 19 - - NC

LVTTL in DATA<8> 22 21 FAULT out LVTTL

LVTTL in DATA<6> 24 23 DATA<7> in LVTTL

LVTTL in CSn 26 25 DATA<5> in LVTTL

LVTTL in SDI 28 27 SCLK in LVTTL

LVTTL in DATA<4> 30 29 SDO out LVTTL

LVTTL in DATA<2> 32 31 DATA<3> in LVTTL

LVTTL in PUSHPL 34 33 DATA<1> in LVTTL

power in GND 36 35 GND in power

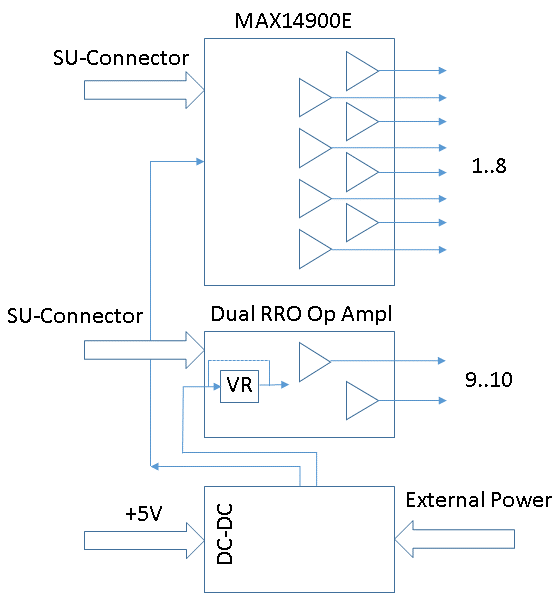

Block diagram:

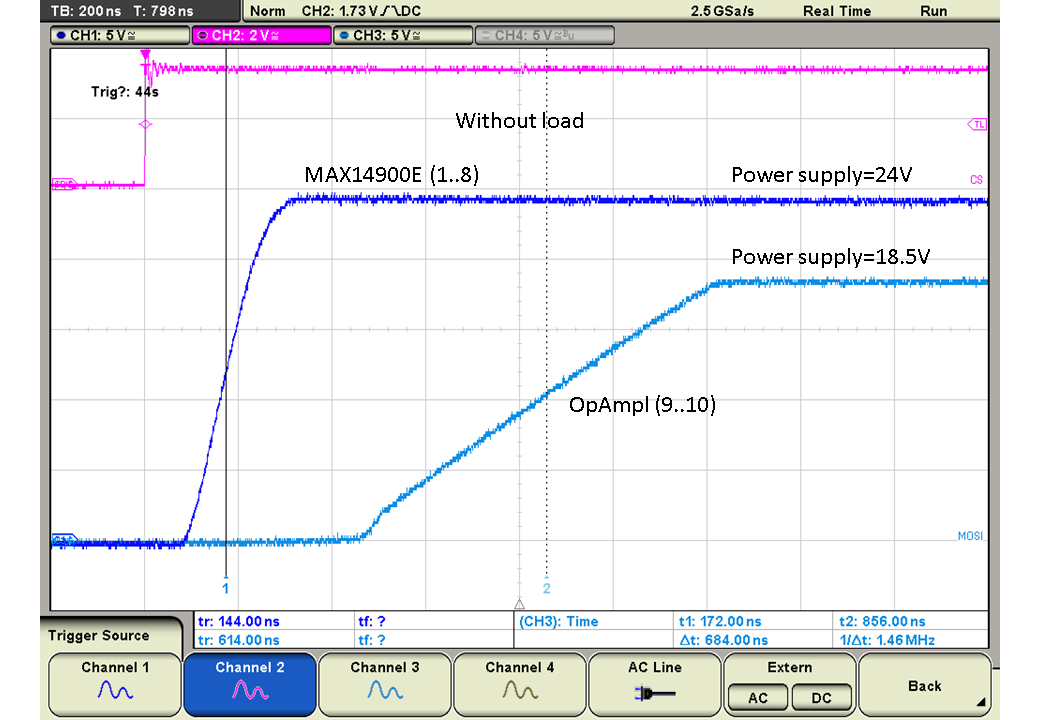

Rising edge, one channel per group, no load:

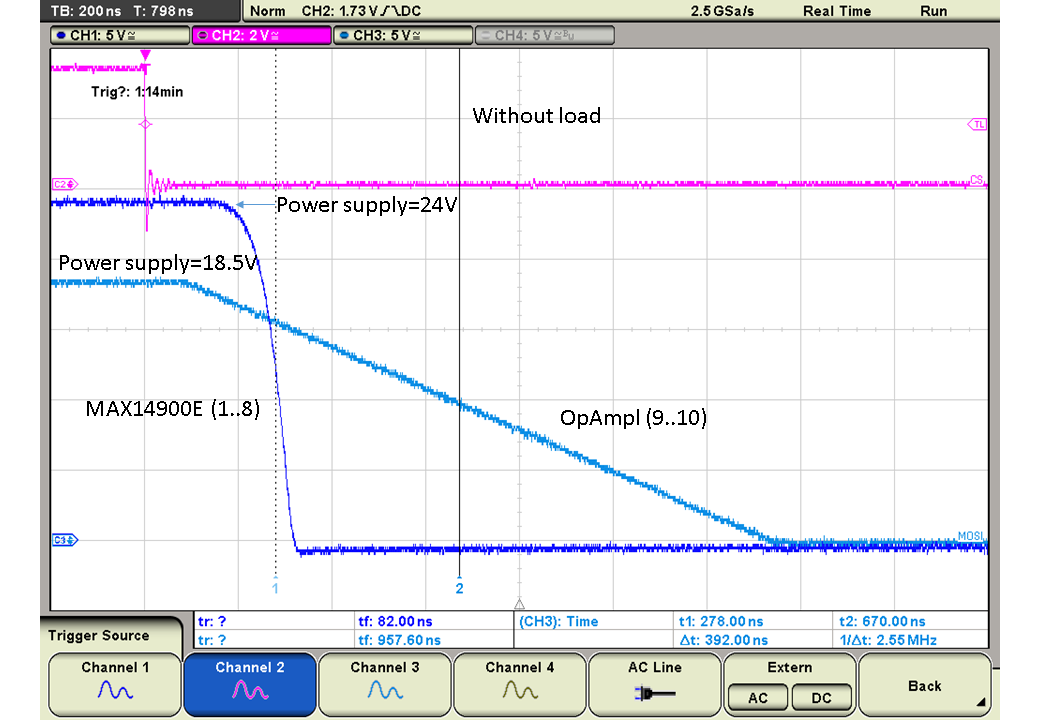

Falling edge, one channel per group, no load:

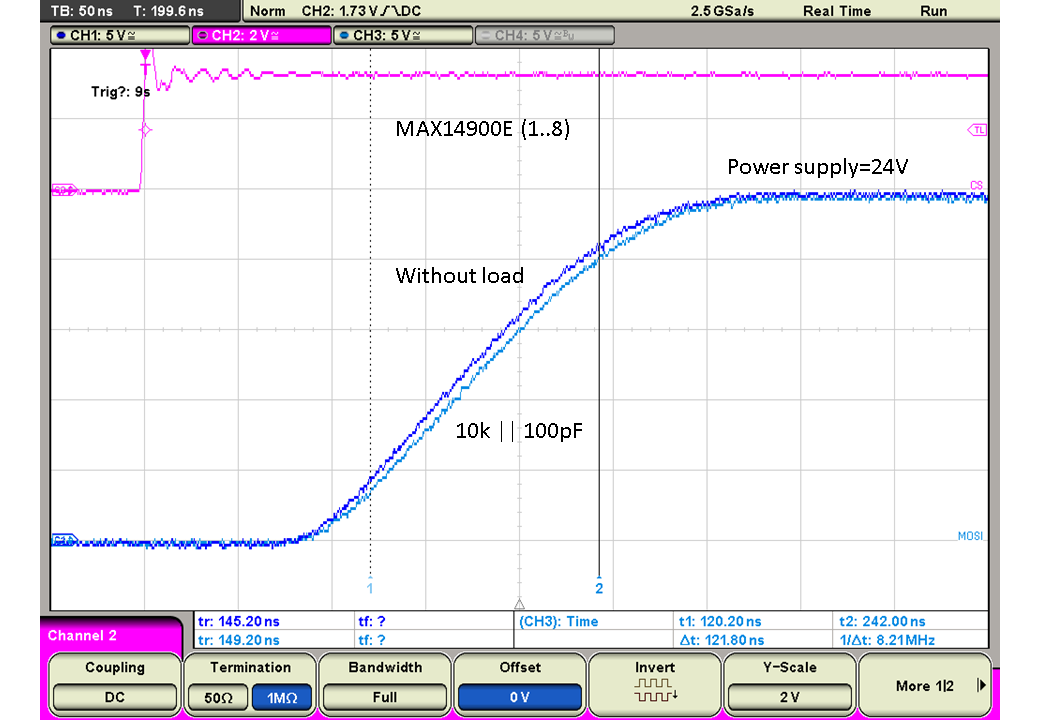

Rising edge, MAX14900E, one channel without load and one channel loaded with 10k || 100pF:

Falling edge, MAX14900E, one channel without load and one channel loaded with 10k || 100pF:

Rising edge, Op Ampl, one channel without load and one channel loaded with 10k || 100pF:

Falling edge, Op Ampl, one channel without load and one channel loaded with 10k || 100pF: