SU753

Contents

- 1 Block diagram

- 2 Pinout

- 3 Measurements

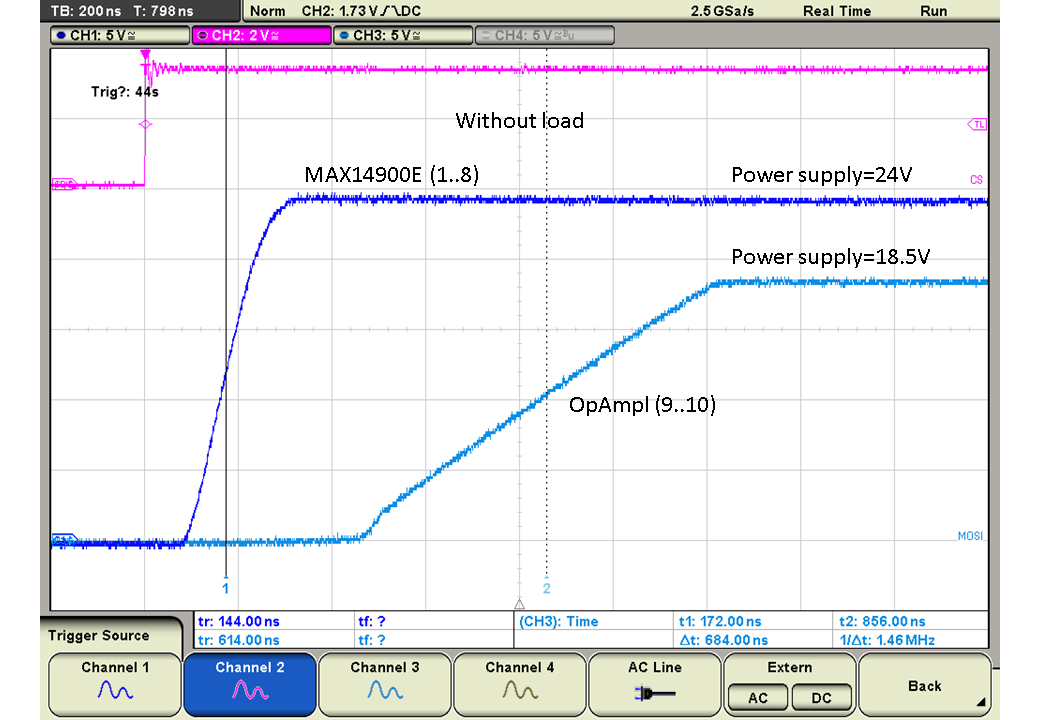

- 3.1 Rising edge, one channel per group, no load

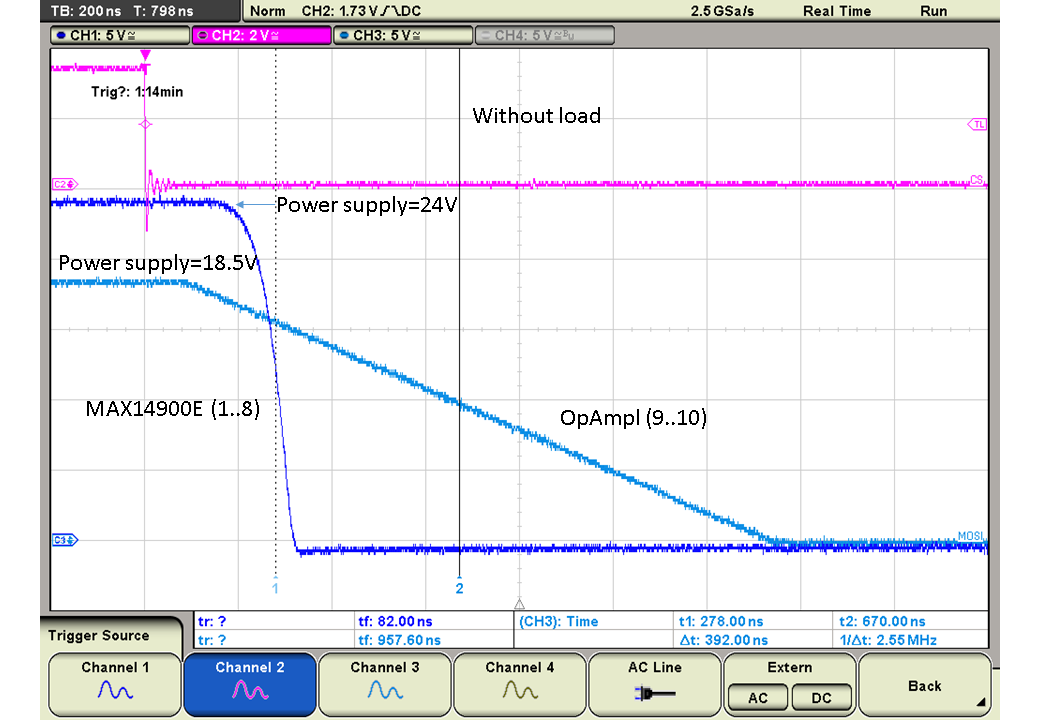

- 3.2 Falling edge, one channel per group, no load

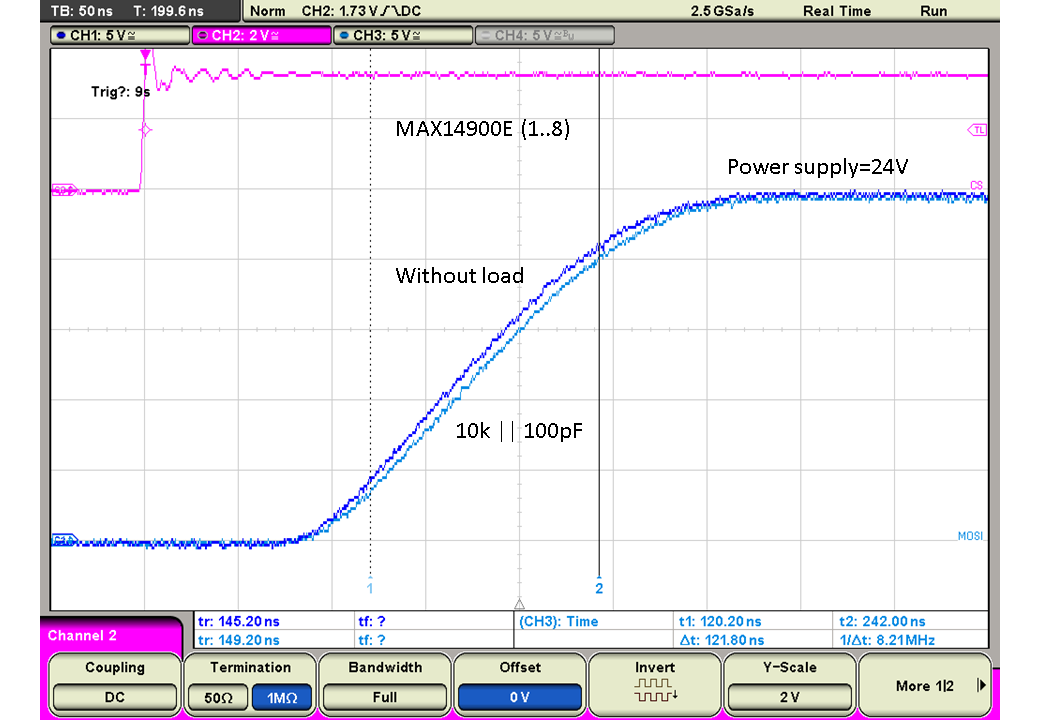

- 3.3 Rising edge, MAX14900E, one channel without load and one channel loaded with 10k || 100pF

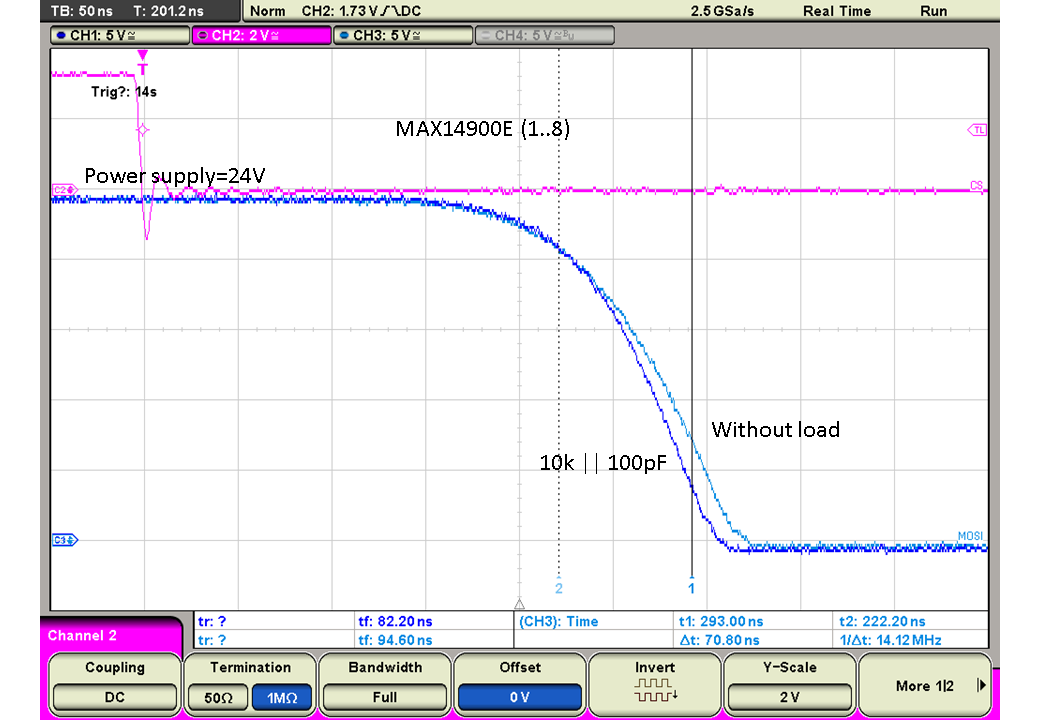

- 3.4 Falling edge, MAX14900E, one channel without load and one channel loaded with 10k || 100pF

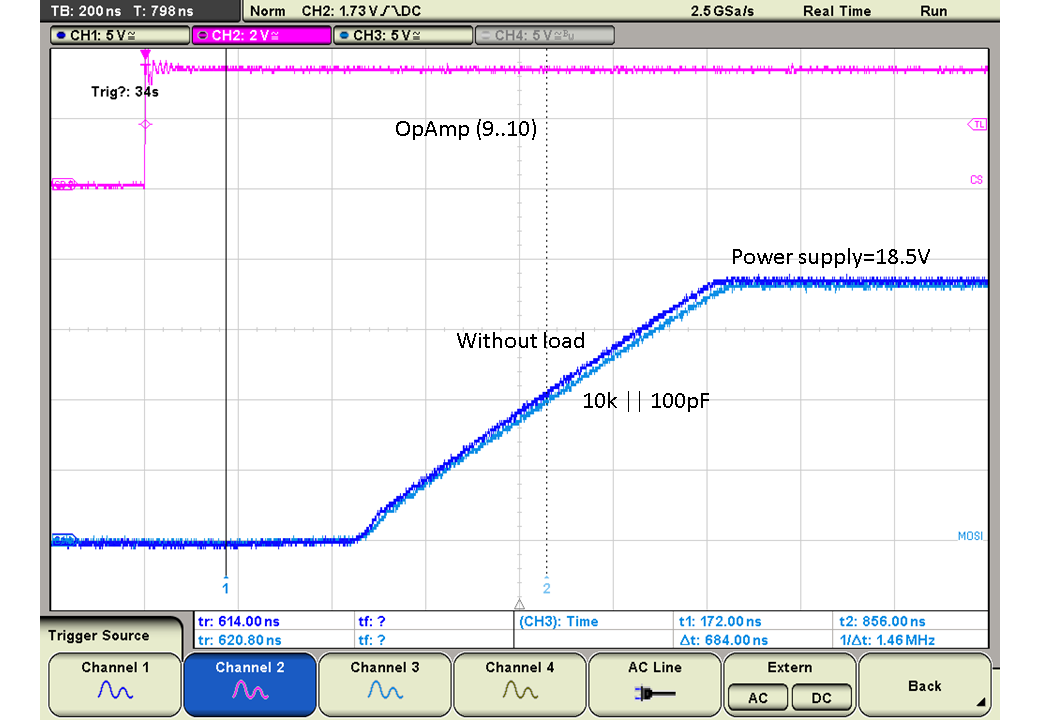

- 3.5 Rising edge, Op Ampl, one channel without load and one channel loaded with 10k || 100pF

- 3.6 Falling edge, Op Ampl, one channel without load and one channel loaded with 10k || 100pF

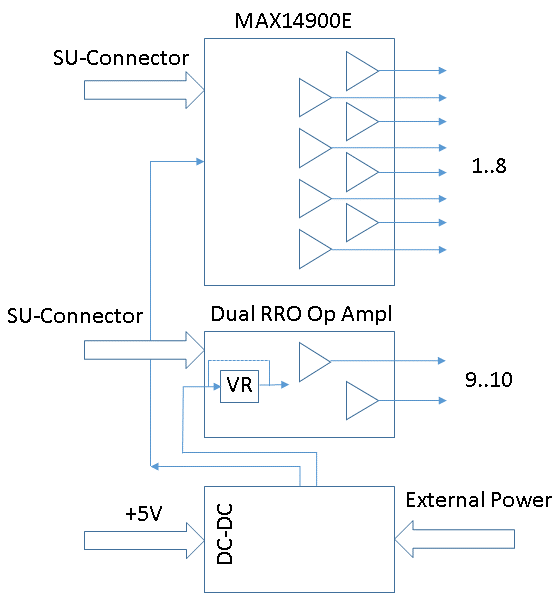

Block diagram

The internal DC-DC Converter can deliver max about 80 mA. If more needed, please use the external power supply.

The MAX14900E chip can drive up to 100 mA per channel, the operational amplifier about 50 mA (but there are serial resistors of 100 Ohm there!). Use the MAX channels for more current.

The voltage supply of the 2 operational amplifier channels can be different from the rest.

The MAX chip has a SPI interface, which is used to read back the status (on|off|failure), see the datasheet for more details. The status of the Op Ampl channels can not be read back!

Pinout

SU753 pin table (direction shown for the SU board!)

power in +5V 2 1 +5V in power

NC - - 4 3 - - NC

NC - - 6 5 - - NC

NC - - 8 7 - - NC

NC - - 10 9 - - NC

NC - - 12 11 - - NC

LVTTL in DATA<10> 14 13 - - NC

LVTTL in DATA<9> 16 15 - - NC

LVTTL in EN 18 17 - - NC

LVTTL in SRIAL 20 19 - - NC

LVTTL in DATA<8> 22 21 FAULT out LVTTL

LVTTL in DATA<6> 24 23 DATA<7> in LVTTL

LVTTL in CSn 26 25 DATA<5> in LVTTL

LVTTL in SDI 28 27 SCLK in LVTTL

LVTTL in DATA<4> 30 29 SDO out LVTTL

LVTTL in DATA<2> 32 31 DATA<3> in LVTTL

LVTTL in PUSHPL 34 33 DATA<1> in LVTTL

power in GND 36 35 GND in power

The two Op Ampl channels 9..10 use only pins DATA<9> and DATA<10>. The other pins control the MAX14900E chip and thus only channels 1..8! The information below is only for channels 1..8:

Some pins have different meaning in SERIAL mode. The present LogicBox designs use the parallel mode (SRIAL=0).

FAULT is open drain and active low, global for the MAX chip.

PSUSHPL is global for the MAX chip and should be 1 for normal operation. Otherwise the MAX outputs will only pull high!

EN is a global pin and should be 1 for normal operation. Single channels can not be enabled/disabled.

The SPI interface in parallel mode is used only to read back the status (on|off|fail) of channels 1..8.