Gate generator (GATEGEN)

Contents

LogicPool (TEMPLATE)

This module does not need any Hardware submodule to work.

Models

There is three model, the only diferent is the width of an internal counter.

Model 0 -> 32 Bits Model 1 -> 24 Bits Model 2 -> 16 Bits

Register Map

Module Address: 'G' or Ox47

Read register

| Register Address | Name | Data |

|---|---|---|

| 0 | VERSION, MODEL and Driver if any |

Bit 31..25: VERSION HI Bit 24..16: VERSION LOW Bit 15..8 : MODEL Bit 7: Status Bit 6..0: Driver |

| 1 | STATUS | Bit 7..0 is the counter active? is running? |

| 2 | COUNTER_VALUE | Bit 31..0 Counter value, the width depends on Model |

Write register

| Register Address | Name | Data |

|---|---|---|

| 0-9 | Input Driver | Bit 7..0: Select the input driver of each output |

Read/Write register

| Register Address | Name | Data |

|---|---|---|

| 16 | CONFIG | Bit 9..0: output register

Bit 25..16: direct input mask |

| 18 | Serial configuration | Serial Config, 15..8 C18..C11, 7..0 C08..C01

Ignored if PUSHPL is high! C1_ C0_ O_ Config OLD 0 High-side mode, open-load detect=OLD X 1 Push-pull mode |

| 19 | Parallel configuration |

Bit 3: PUSHPL - this is the global pin, if low, then can be set pin by pin using SPI

high means the outputs 7..0 are push-pull, low - depending on the serial config

Bit 2: unused

Bit 1: SRIAL - low for parallel mode, hardwired now!

Bit 0: global enable for outputs 7..0 (8..1)

|

LabVIEW Vi

TEMPLATE.vi

Template VI for new designs

Introduction.

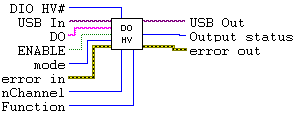

The meaning of almost inputs and outputs of this Vi depends on the input "Function". The global inputs and outputs does not depend on the "function" input:

Glogal Inputs

DIO_HV#: number of HV digital output to be accesed (1..255).

USB In: Handle to the LogicBox (create by open.vi), if not connected will take a global. parameter, this only works with one LogicBox at a time.

error in: error handling input

Global Outputs

USB out: Handle to the LogicBox.

error out: error handling output

Functions

Connect: enable, configurate and set input/value of the HV digital output.

Inputs:

"DO" : set the signal number which will drive the output, this signal can be set or clear

manually using the module "B_S.vi" (Bool to Signal).

"DI" : get the signal number of which drives this input.

Get Status: the cicuitry of the digital output can detect two errors, under voltage or logic state

undifined. Only the first 8 channels support this features

Input: "Channel": number of channel to be configured

Output: Output Status

Set DO: set the signal number which will drive the output, this signal can be set or clear manually

using the module "B_S.vi" (Bool to Signal).

Input: "Channel": number of channel to be configured

"DO" set the signal number which will set the output value.

Example VIs

SU7XX_XX_test.vi