SU736

Description

Block Diagram

Version 0

Front planel

| Pos (top view) | Name | Type | Qty. | Dir. | Function |

|---|---|---|---|---|---|

| 1 LEFT | Analog input | LEMO connector | 1x | input | Analog input to compare channel 1 |

| 1 RIGHT | LED 1 | LED | 1x | status LED driven from FPGA | |

| 2 LEFT | Analog input | LEMO connector | 1x | input | Analog input to compare channel 2 |

| 2 RIGHT | LED 2 | LED | 1x | status LED driven from FPGA | |

| 3 MIDDLE | Threshold 1 | Potentiometer | 1x | input | Set the threshold of the comparator 1, you can choose between a DAC or this potentiometer (jumper option) |

| 4 MIDDLE | Threshold 2 | Potentiometer | 1x | input | Set the threshold of the comparator 2, you can choose between a DAC or this potentiometer (jumper option) |

| 5 LEFT | DIO | LEMO connector | 1x | output | Digital output NIM, connect to discriminator output 1 |

| 5 RIGHT | LED 3 | LED | 1x | status LED driven from FPGA | |

| 6 LEFT | DIO | LEMO connector | 1x | output | Digital output NIM, connect to discriminator output 2 |

| 6 RIGHT | LED 4 | LED | 1x | status LED driven from FPGA |

Back Connector

SU736 pin table (direction shown for the SU board!)

power in +5V 2 1 +5V in power

NC - - 4 3 - - NC

NC - - 6 5 - - NC

LVTTL out CMP_SE<2> 8 7 - - NC

NC - - 10 9 - - NC

LVTTL out CMP_SE<1> 12 11 - - NC

NC - - 14 13 - - NC

LVDS_n out CMP_Dn<2> 16 15 CMP_Dp<2> out LVDS_p

LVDS_n out CMP_Dn<1> 18 17 CMP_Dp<1> out LVDS_p

NC - - 20 19 - - NC

NC - - 22 21 - - NC

LVTTL in CS_DACn 24 23 SCLK_DAC in LVTTL

LVTTL in SDI_DAC 26 25 - - NC

NC - - 28 27 - - NC

LVTTL in LED_CMPn<1> 30 29 LED_CMPn<2> in LVTTL

LVTTL in LED_NIMn<1> 32 31 LED_NIMn<2> in LVTTL

NC - - 34 33 - - NC

power in GND 36 35 GND in power

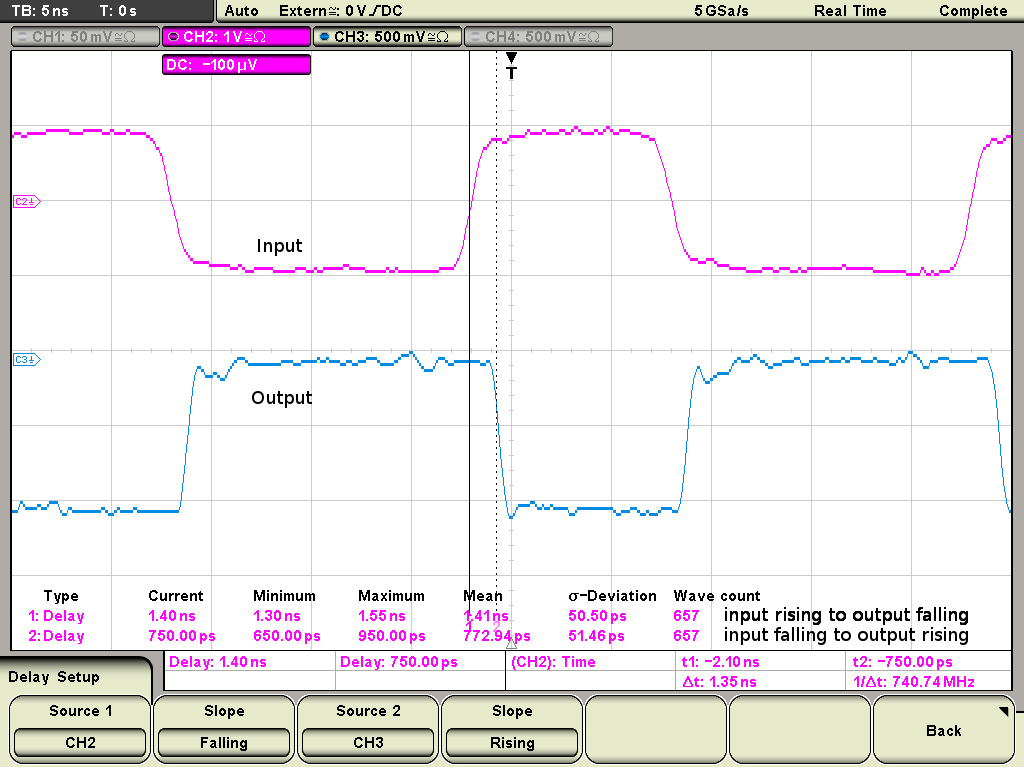

Measurement

Measurement of the input-output delay